### **Timing Analysis of Software Executing** on Undocumented Multicore Processors

**Bjorn Andersson**

Software Engineering Institute Carnegie Mellon University Pittsburgh, PA 15213

**Carnegie Mellon University**

Software Engineering Institute

[DISTRIBUTION STATEMENT A] This material has been approved for public release and unlimited distribution.

Copyright 2019 Carnegie Mellon University. All Rights Reserved.

This material is based upon work funded and supported by the Department of Defense under Contract No. FA8702-15-D-0002 with Carnegie Mellon University for the operation of the Software Engineering Institute, a federally funded research and development center.

NO WARRANTY. THIS CARNEGIE MELLON UNIVERSITY AND SOFTWARE ENGINEERING INSTITUTE MATERIAL IS FURNISHED ON AN "AS-IS" BASIS. CARNEGIE MELLON UNIVERSITY MAKES NO WARRANTIES OF ANY KIND, EITHER EXPRESSED OR IMPLIED, AS TO ANY MATTER INCLUDING, BUT NOT LIMITED TO, WARRANTY OF FITNESS FOR PURPOSE OR MERCHANTABILITY, EXCLUSIVITY, OR RESULTS OBTAINED FROM USE OF THE MATERIAL. CARNEGIE MELLON UNIVERSITY DOES NOT MAKE ANY WARRANTY OF ANY KIND WITH RESPECT TO FREEDOM FROM PATENT, TRADEMARK, OR COPYRIGHT INFRINGEMENT.

[DISTRIBUTION STATEMENT A] This material has been approved for public release and unlimited distribution. Please see Copyright notice for non-US Government use and distribution.

This material may be reproduced in its entirety, without modification, and freely distributed in written or electronic form without requesting formal permission. Permission is required for any other use. Requests for permission should be directed to the Software Engineering Institute at permission@sei.cmu.edu.

DM19-0890

**SBESC** 2019

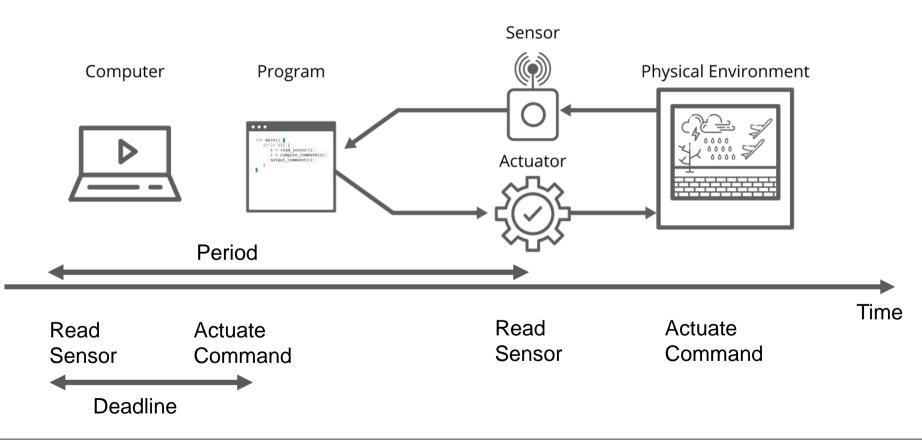

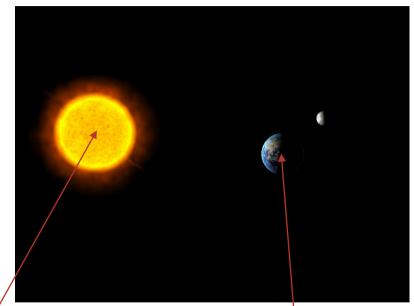

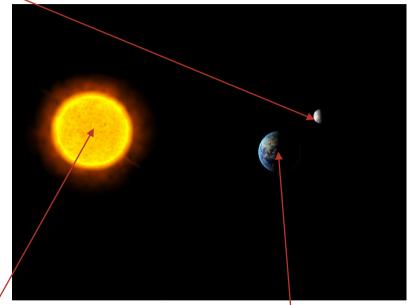

### Systems Interact with Their Physical Environment

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

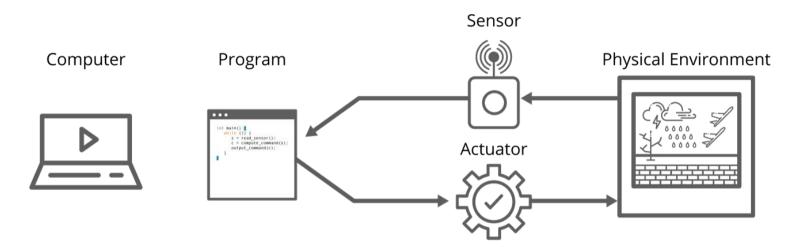

#### Systems Include Software

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

#### Systems Include Software That Interacts with the Physical Environment

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

#### Systems Include Software That Has Real-Time Requirements

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

```

SBESC 2019

```

# Satisfying Real-Time Requirements is a Challenge for These Systems in General

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

```

SBESC 2019

```

"The trick there, when you're processing flight critical information, it has to be a deterministic environment, meaning we know exactly where a piece of data is going to be exactly when we need to — no room for error," Langhout says. "On a multi-core processor there's a lot of sharing going on across the cores, so right now we're not able to do that." - Jeff Langhout, Acting Director, U.S. Army Aviation and Missile Research Development and Engineering Center (AMRDEC)

Source: "Army still working on multi-core processor for UH-60V," May 2017, Available at https://www.flightglobal.com/news/articles/army-still-working-on-multi-core-processor-for-uh-6-436895/.

```

SBESC 2019

```

"A majority of avionics today are running on single-core processors, or multicore processors with all but one core disabled."

"The root of the problem is shared resources, which most of the time creates some kind of interference."

Source: "It's time: Avionics need to move to multicore processors," January 2018, Available at http://www.intelligent-aerospace.com/articles/2018/01/it-s-time-avionics-needs-to-move-to-multicore-processors.html.

```

SBESC 2019

```

"In safety-critical domains such as avionics, the multicore "predictability problem" is currently dealt with by turning off all but one core if highly-critical system components exist."

Source: C. J. Kenna et al., "Making Shared Caches More Predictable on Multicore Platforms," RTSS'2012.

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

```

SBESC 2019

```

"Currently, avionics manufacturers resolve the multicore "predictability problem" by turning off all but one core if highly critical system components exist."

Source: B. C. Ward et al., "Making Shared Caches More Predictable on Multicore Platforms," ECRTS'2013.

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

Ę

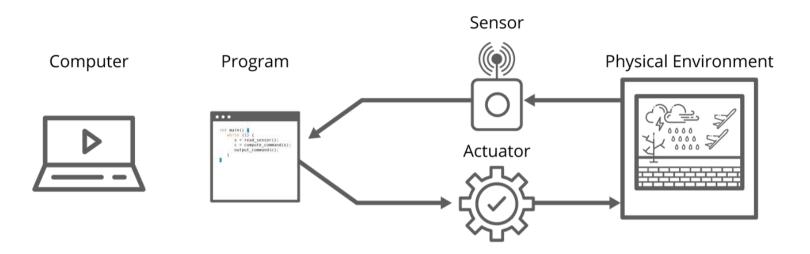

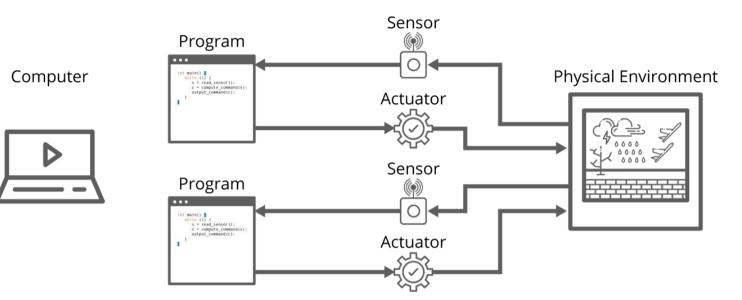

### Commonality of these Systems

Ę

### Commonality of these Systems

|         | Time               |

|---------|--------------------|

| Actuate |                    |

|         |                    |

| Commanu |                    |

|         | Actuate<br>Command |

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

╘┯═

### Commonality of these Systems

╘┯═

### Commonality of these Systems

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

**SBESC** 2019

Ę

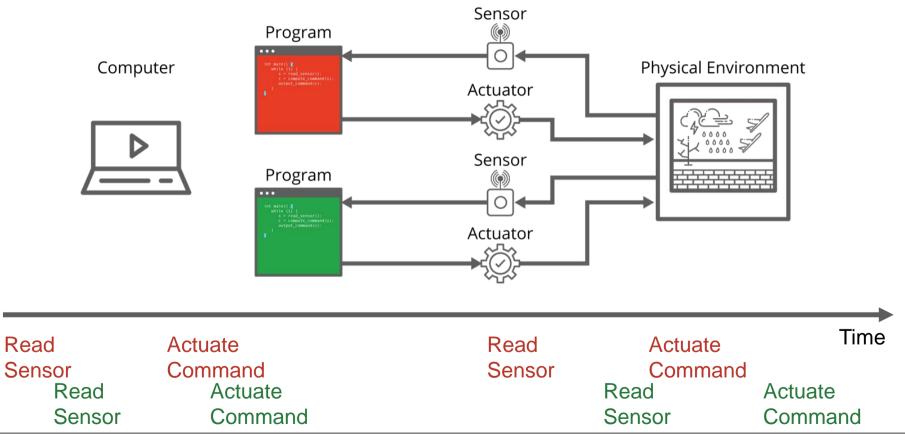

### Commonality of these Systems

╘┯═

### Commonality of these Systems

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

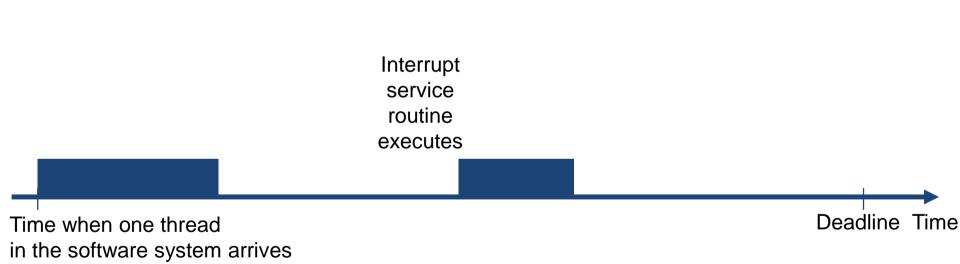

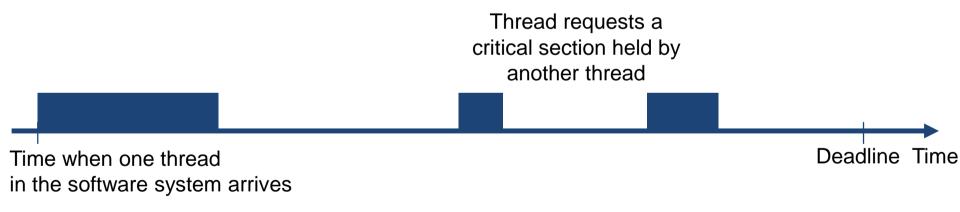

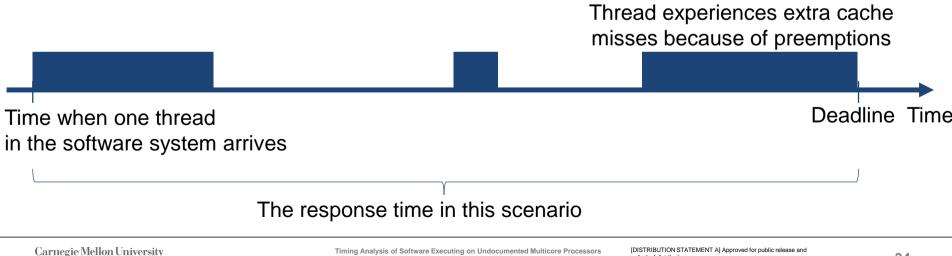

#### What Makes it Challenging to Satisfy Real-Time Requirements?

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

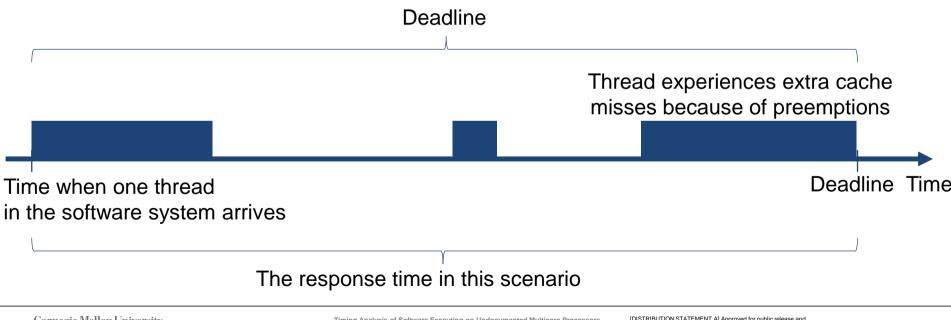

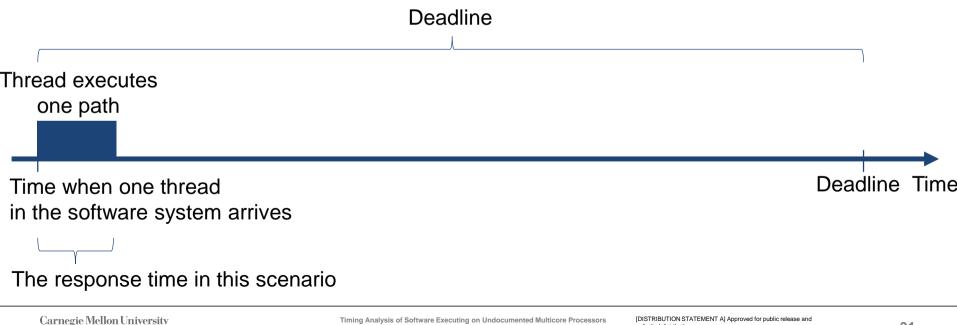

Time when one thread in the software system arrives

Deadline Time

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

Time when one thread in the software system arrives

Deadline Time

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

Thread executes another path

Time when one thread in the software system arrives

Deadline Time

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

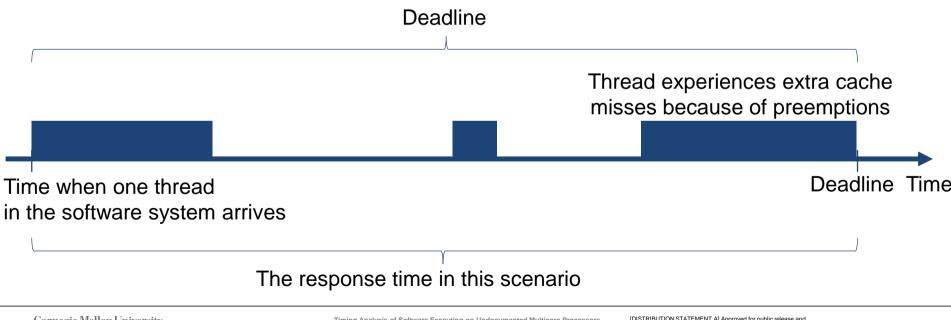

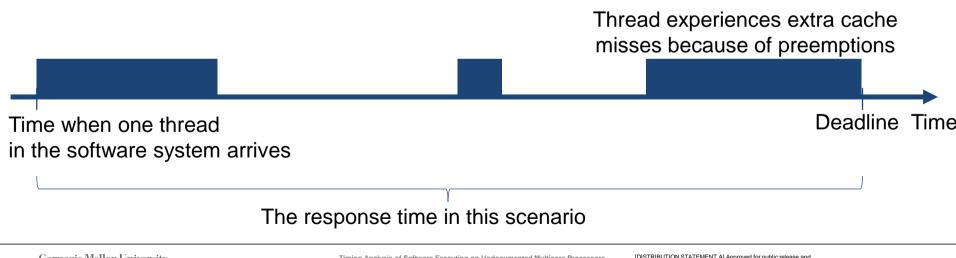

Preemption: Another thread uses the processor.

Time when one thread in the software system arrives

Deadline Time

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

How large can the response time be?

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

#### Does it hold for all scenarios that the response time is at most the deadline?

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

Does it hold for all scenarios that the response time is at most the deadline?

Software Engineering Institute

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

#### Does it hold for all scenarios that the response time is at most the deadline?

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

Does it hold for all threads, that for all arrivals of the thread, that for all scenarios, that the finishing time is at most the deadline?

**Carnegie Mellon University** Software Engineering Institute

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

SBESC 2019

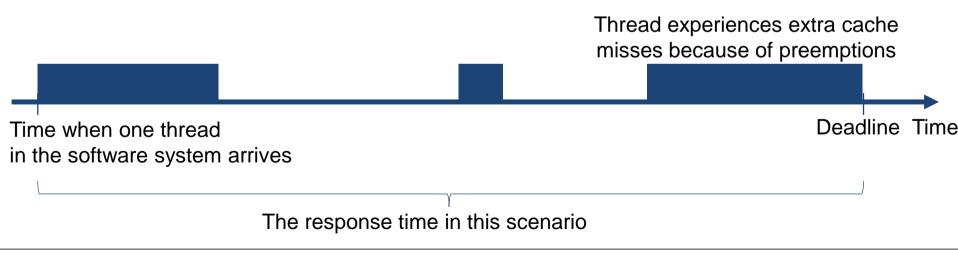

#### What Causes Delay of Software?

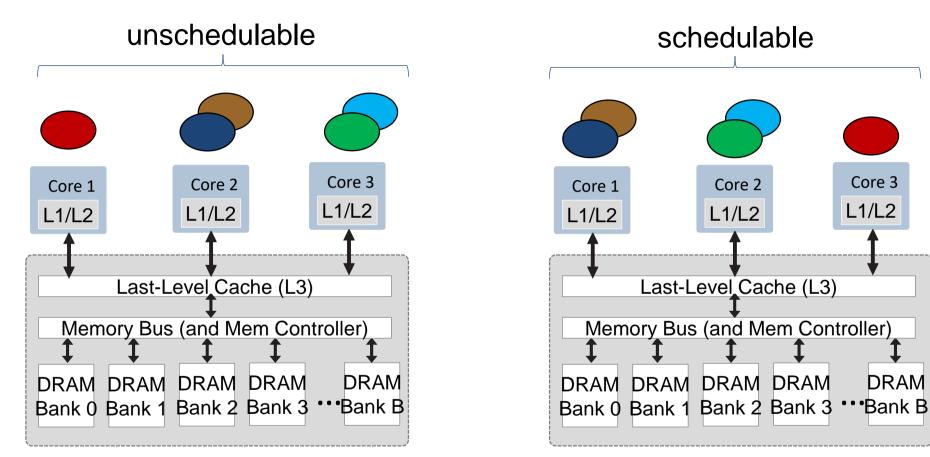

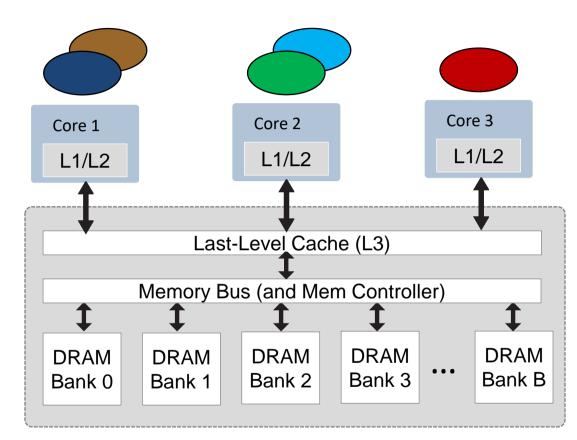

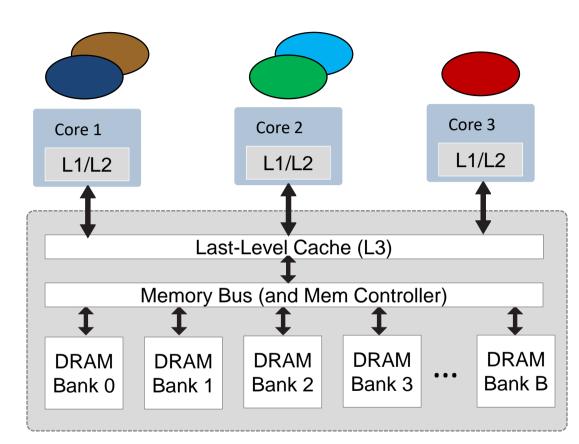

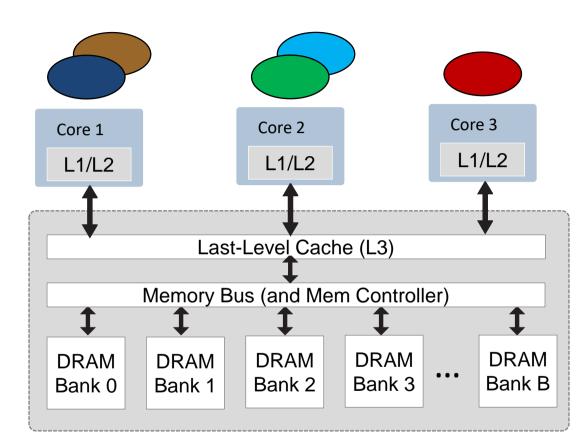

Does it hold for all threads. that for all arrivals of the thread. that for all scenarios. that the finishing time is at most the deadline?

If "yes," we say the set of threads is *schedulable*. Otherwise, the set of threads is unschedulable.

SBESC 2019

#### What Causes Delay of Software?

Does it hold for all threads, that for all arrivals of the thread, that for all scenarios, that the finishing time is at most the deadline?

If "yes," we say the set of threads is *schedulable*. Otherwise, the set of threads is *unschedulable*.

The process of determining whether a set of threads is schedulable is called *schedulability analysis*.

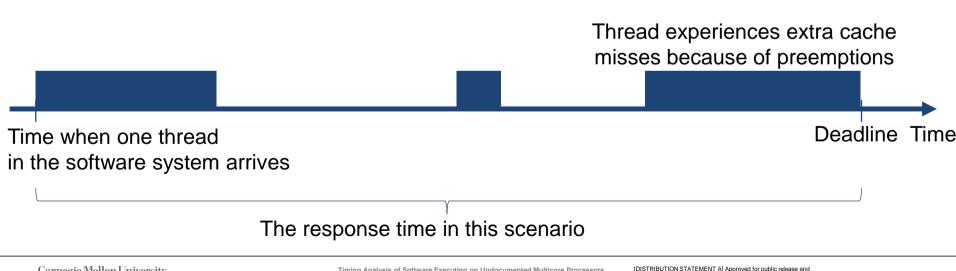

Thread experiences extra cache misses because of preemptions

Time when one thread in the software system arrives

#### The response time in this scenario

**Carnegie Mellon University** Software Engineering Institute

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

Time

Deadline

### Conclusions so far

Many systems interact with the physical world

This interaction requires correct timing

Correct timing depends on the whether the delay of the software is at most a certain bound

There are many causes of the delay of software (even on a computer with a single core)

Many systems today disable all processor cores except one in order to be confident about timing

**SBESC** 2019

### Real-Time Requirements of Software Executing on a Multicore Processor

Hardware Trends

• All computers are multicores.

**SBESC** 2019

### Real-Time Requirements of Software Executing on a Multicore Processor

Hardware Trends

- All computers are multicores.

- Most chip makers do not offer single core.

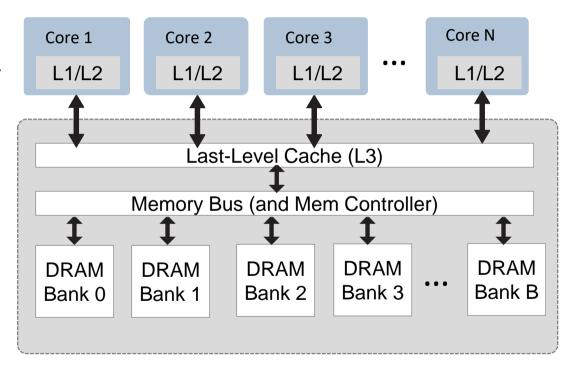

### Real-Time Requirements of Software Executing on a Multicore Processor

Hardware Trends

- All computers are multicores.

- Most chip makers do not offer single core.

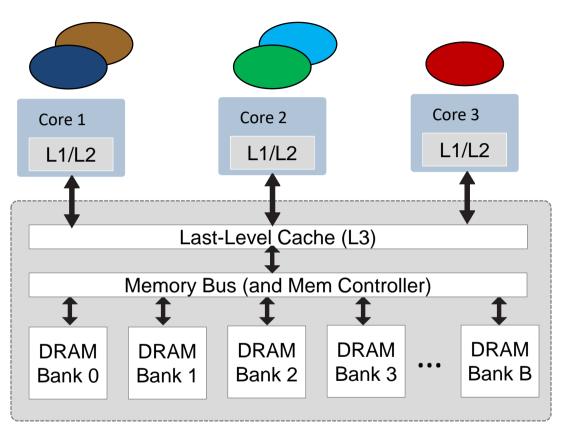

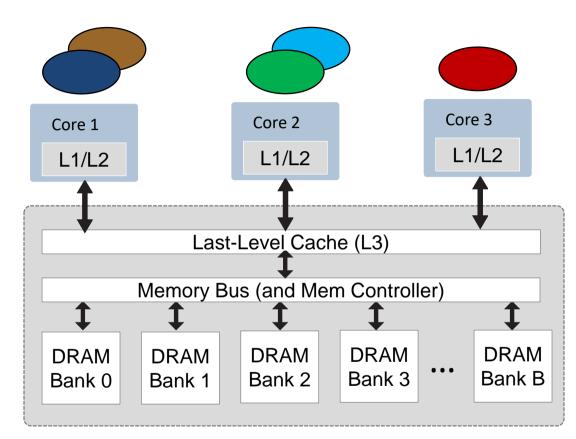

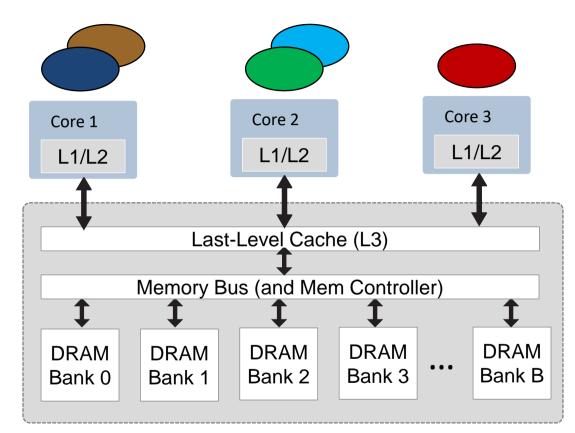

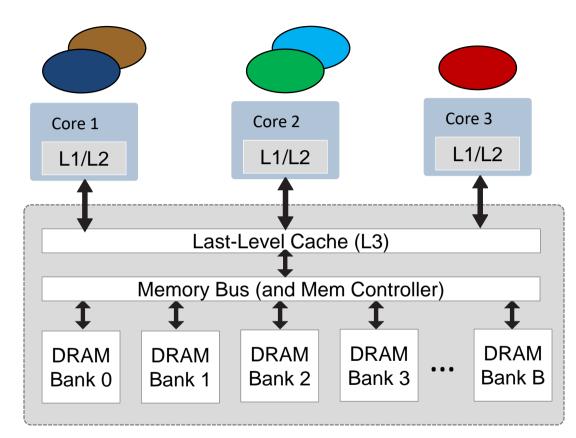

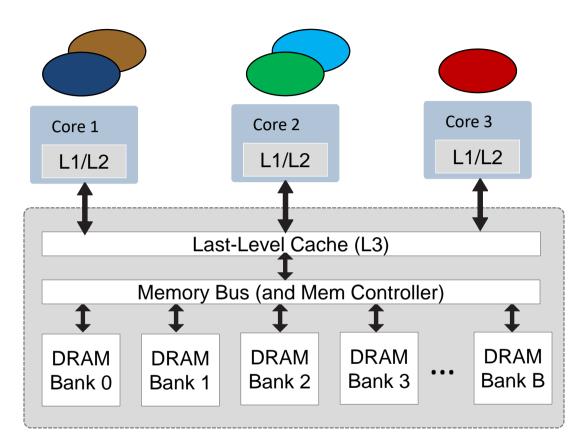

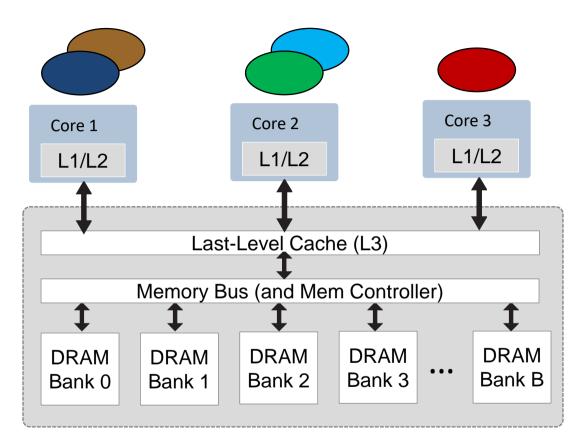

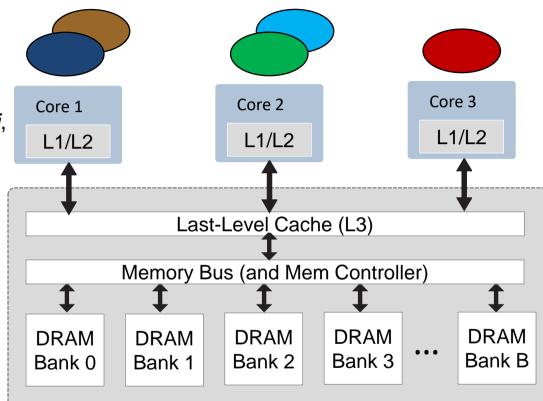

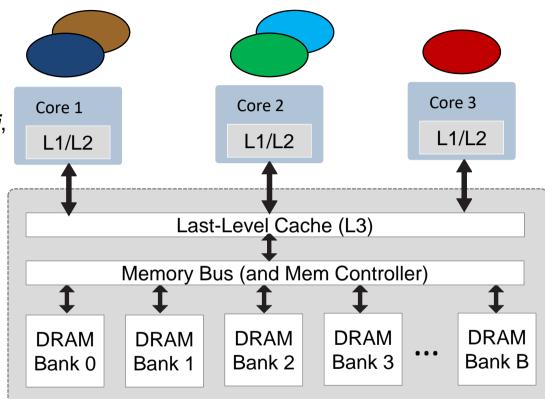

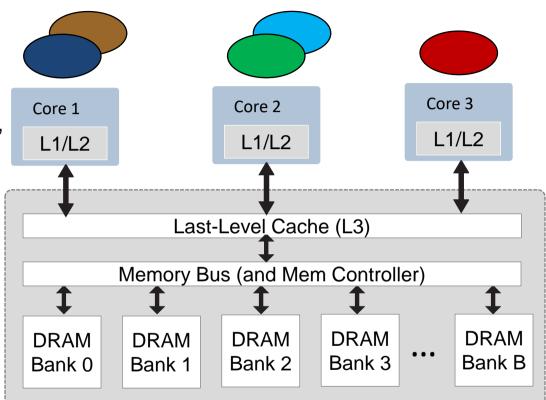

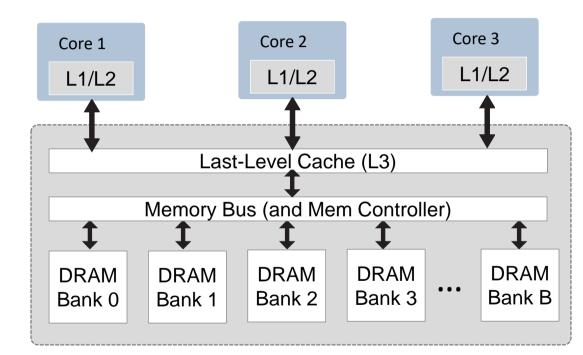

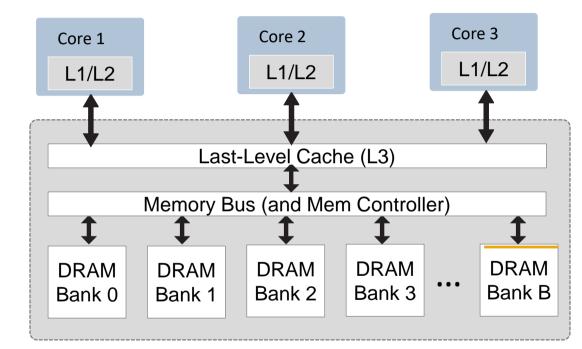

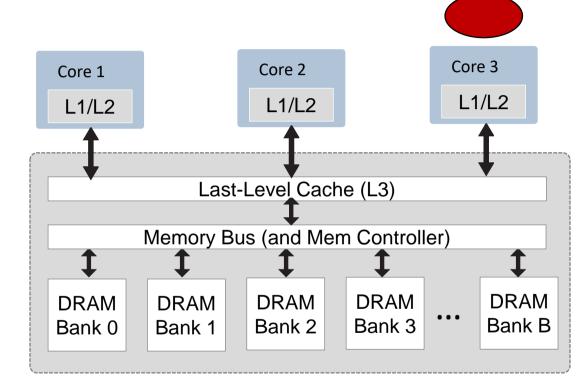

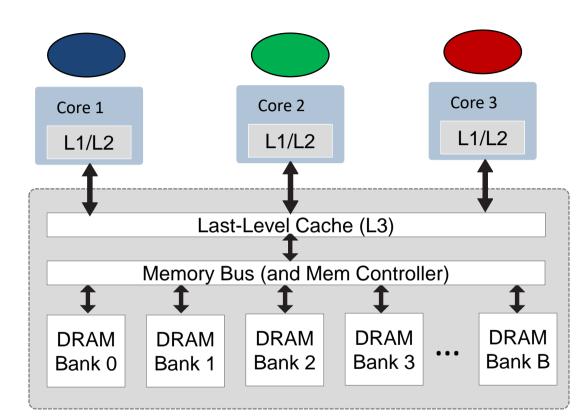

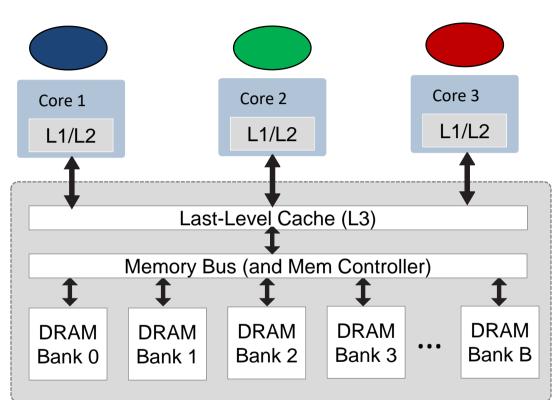

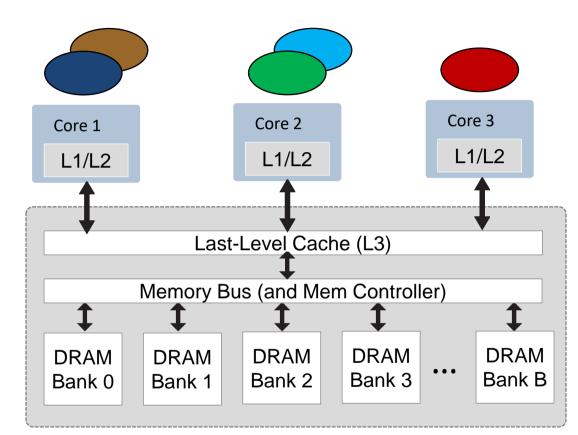

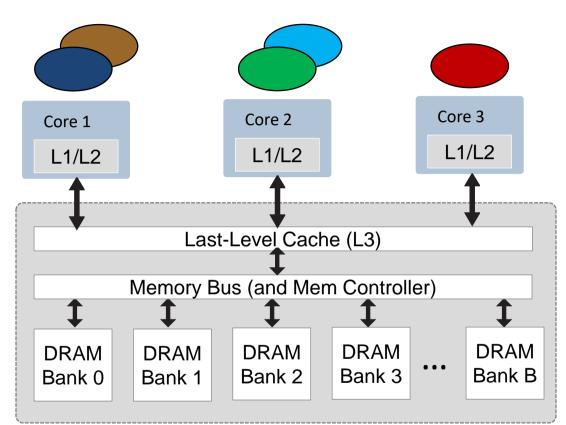

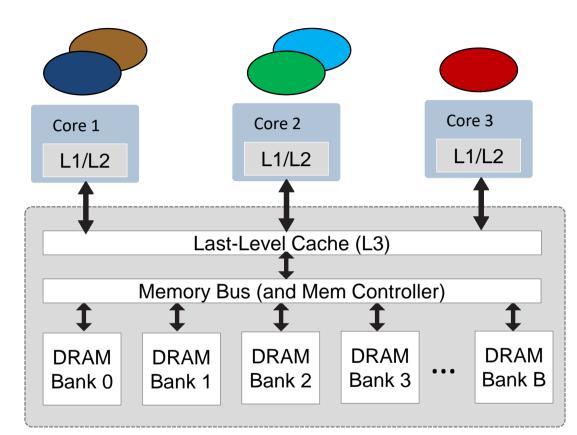

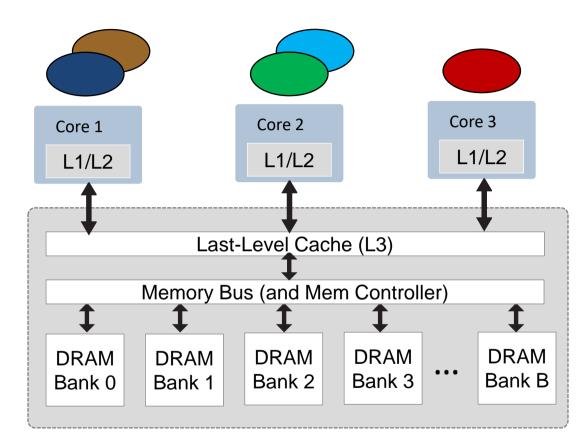

- Most multicores have shared memory.

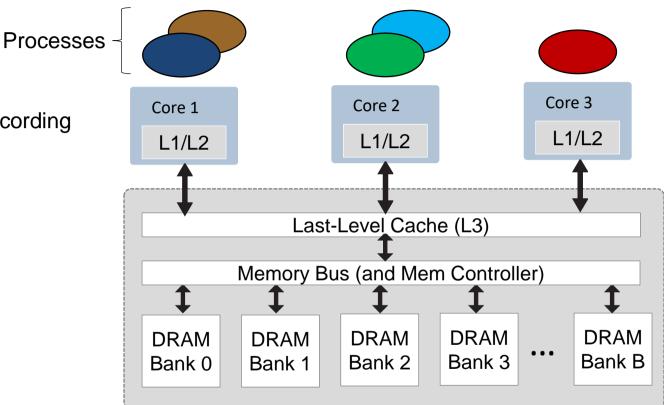

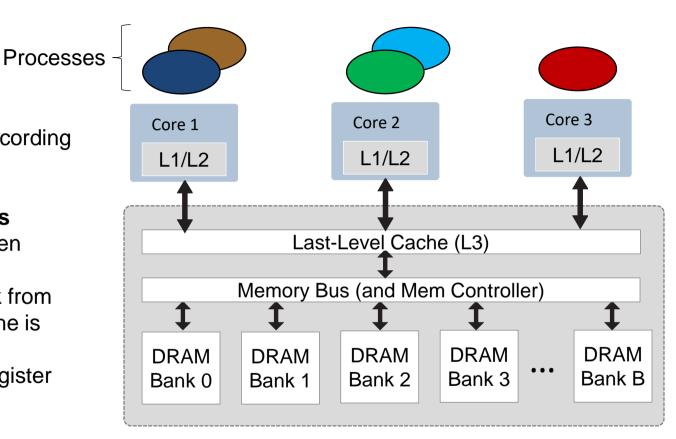

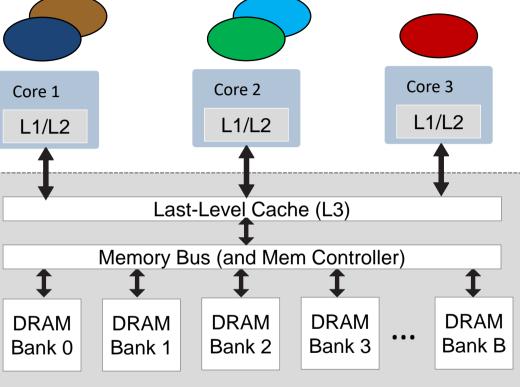

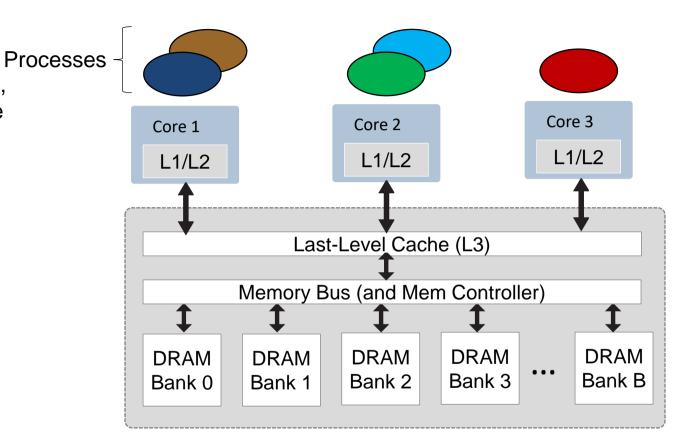

**Problem:** For each process, compute an upper bound on its response time.

#### **SBESC** 2019

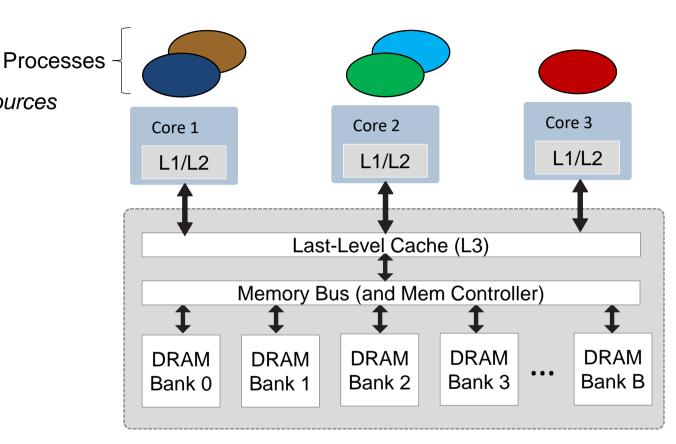

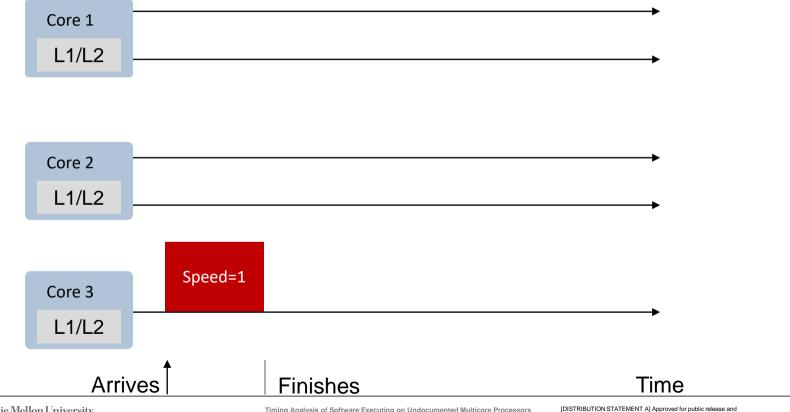

### How Co-Runners Impact Speed of Execution

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release ar unlimited distribution.

#### **SBESC** 2019

### How Co-Runners Impact Speed of Execution

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release and unlimited distribution.

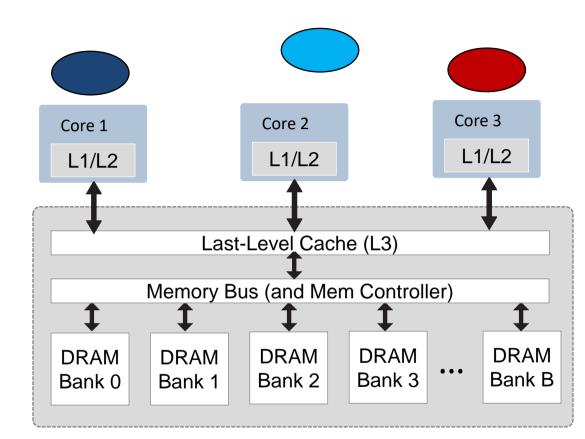

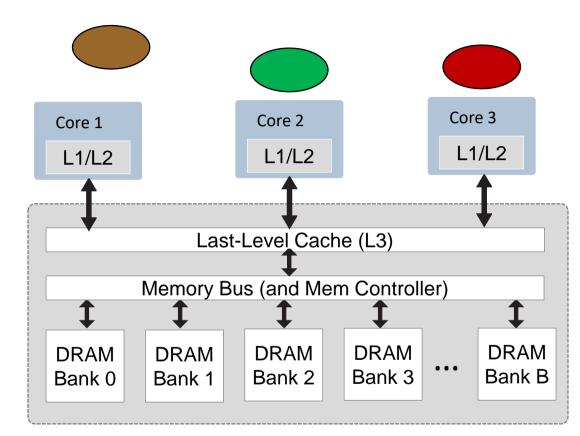

**Problem:** For each process, compute an upper bound on its response time.

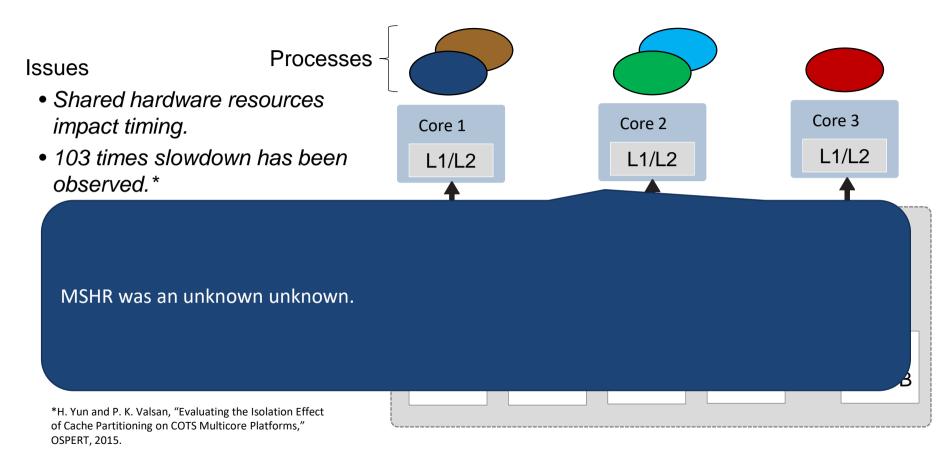

• Shared hardware resources impact timing.

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release and unlimited distribution.

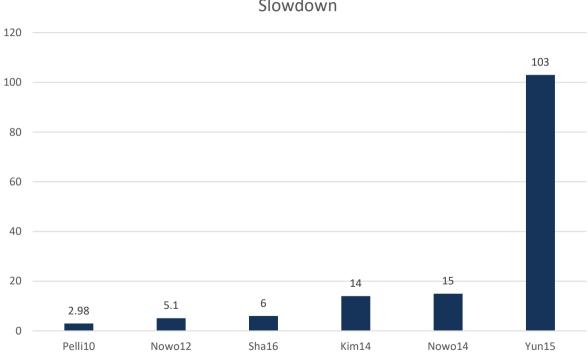

Slowdown

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release and unlimited distribution.

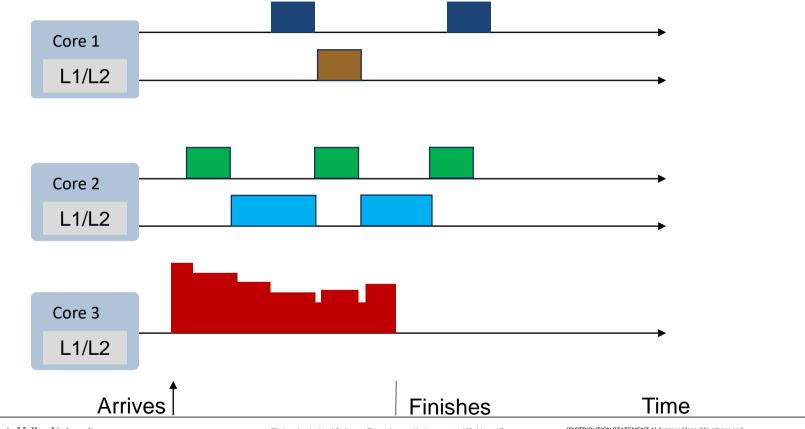

- Shared hardware resources impact timing.

- 103 times slowdown has been observed.\*

\*H. Yun and P. K. Valsan, "Evaluating the Isolation Effect of Cache Partitioning on COTS Multicore Platforms," OSPERT, 2015.

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

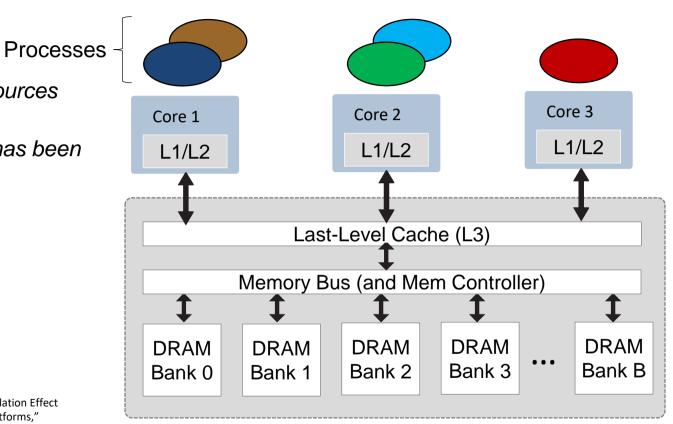

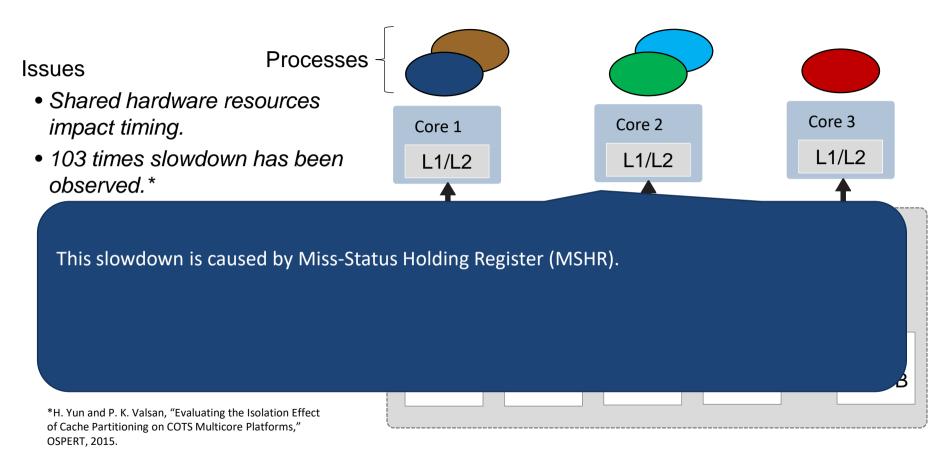

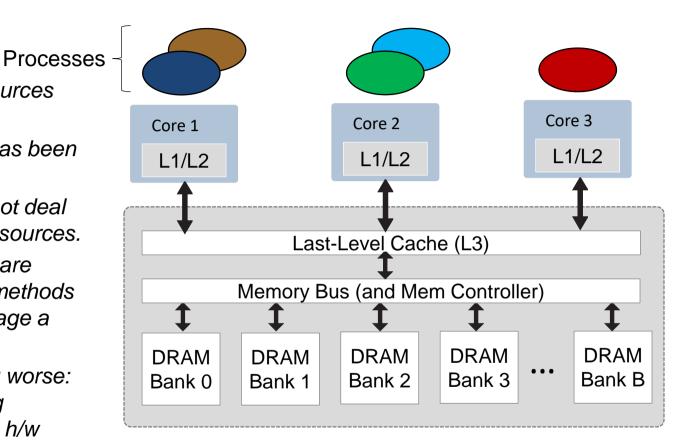

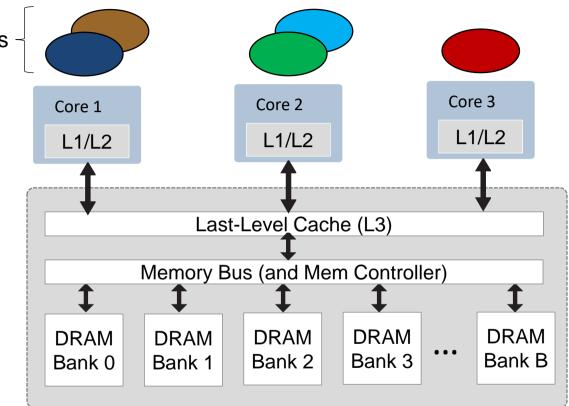

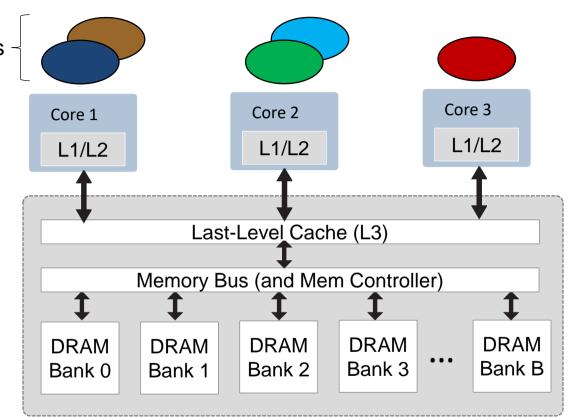

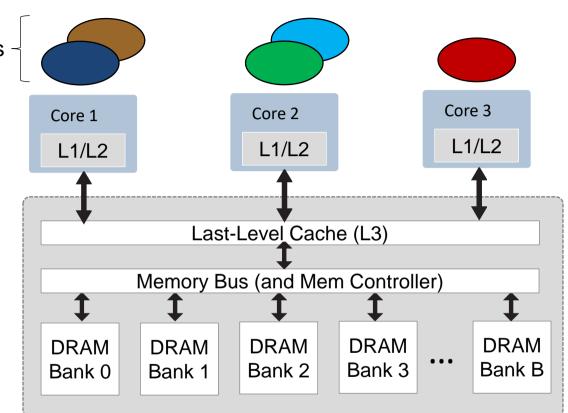

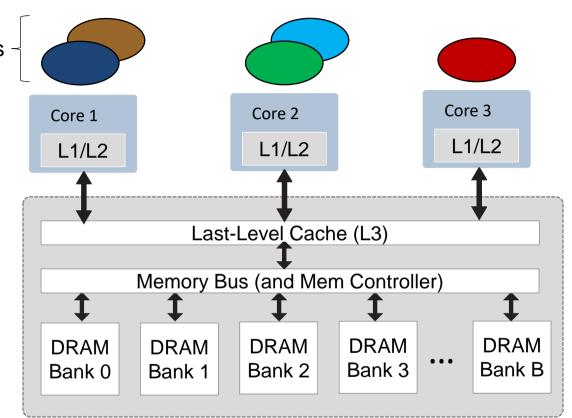

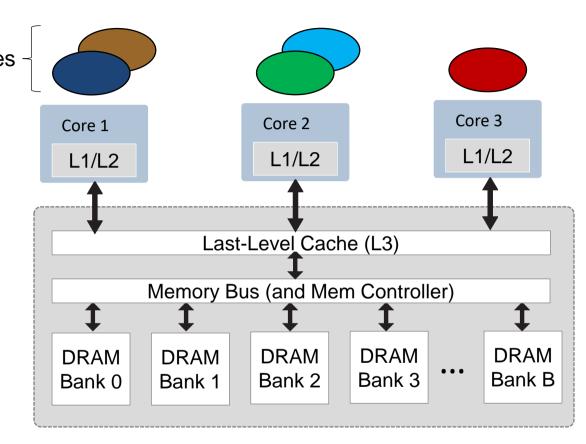

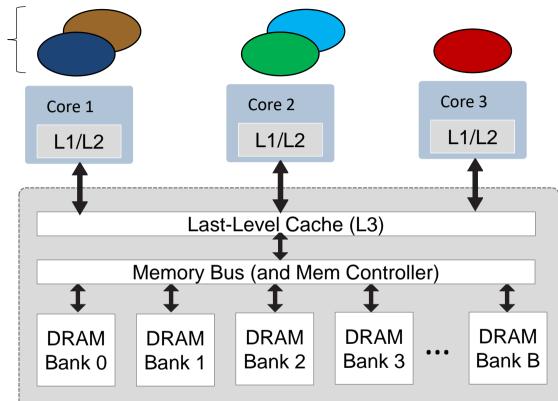

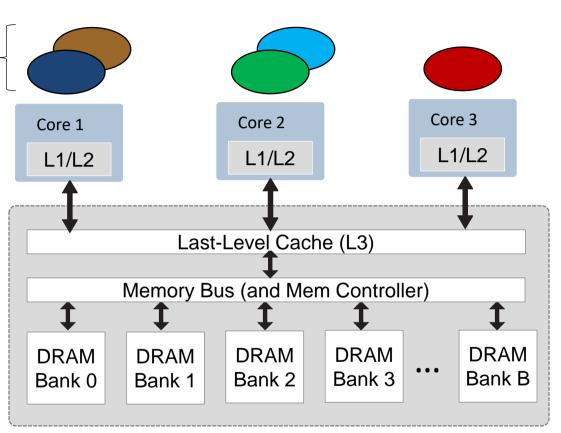

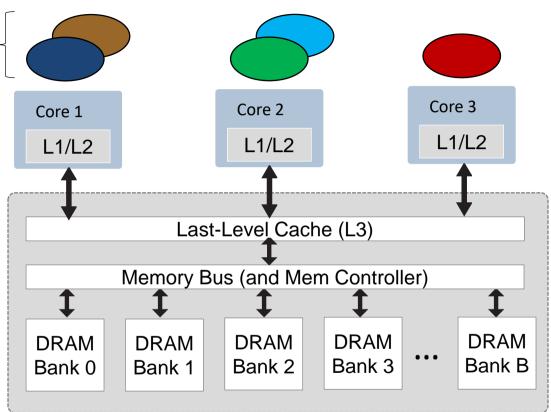

- Shared hardware resources impact timing.

- 103 times slowdown has been observed.\*

This slowdown is caused by Miss-Status Holding Register (MSHR). At that time, most researchers in real-time systems community were not aware of the MSHR.

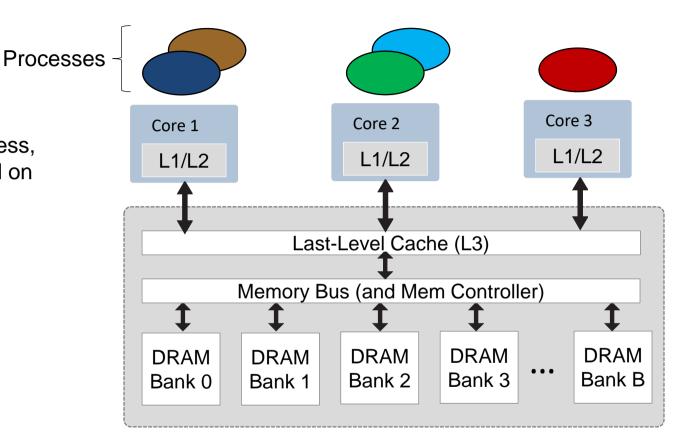

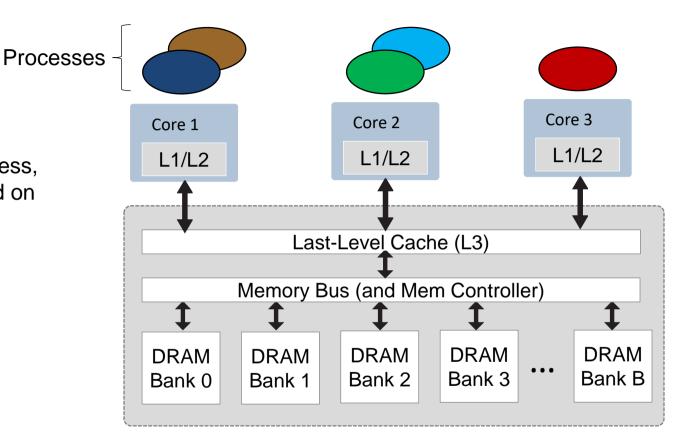

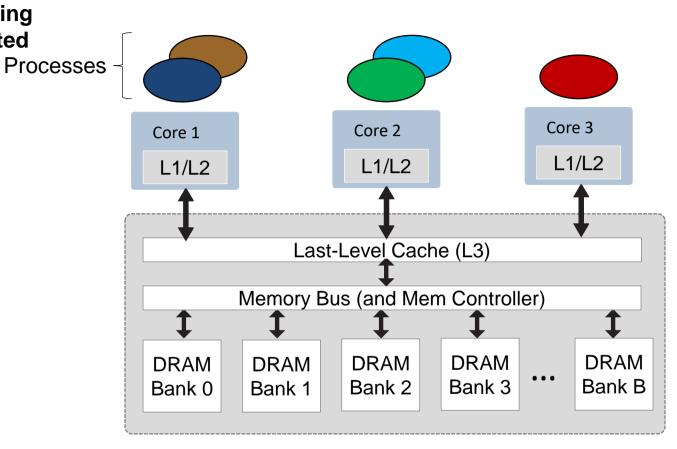

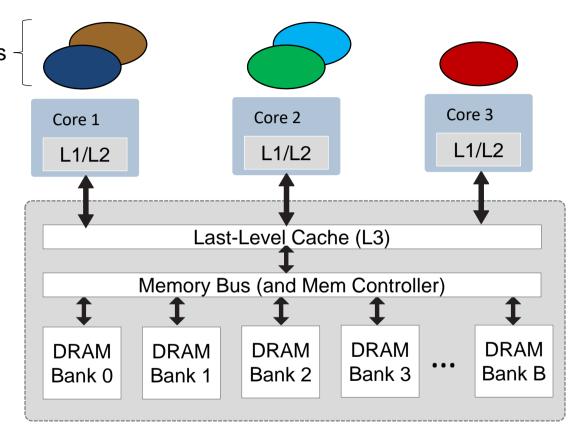

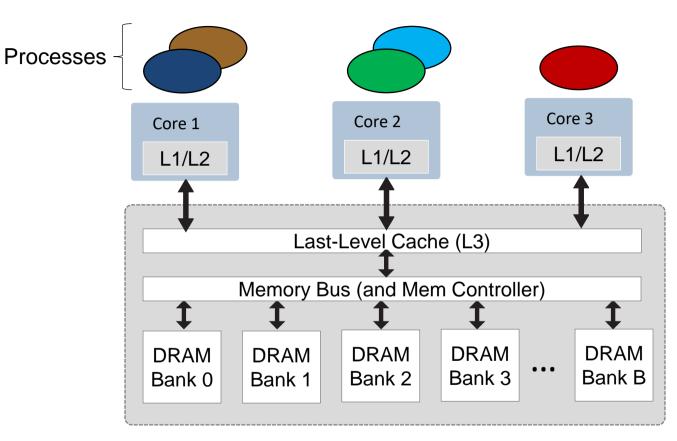

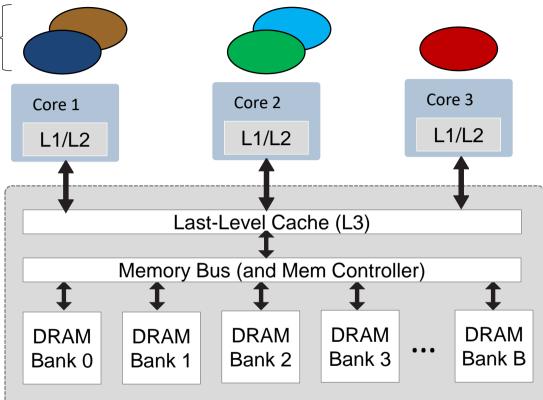

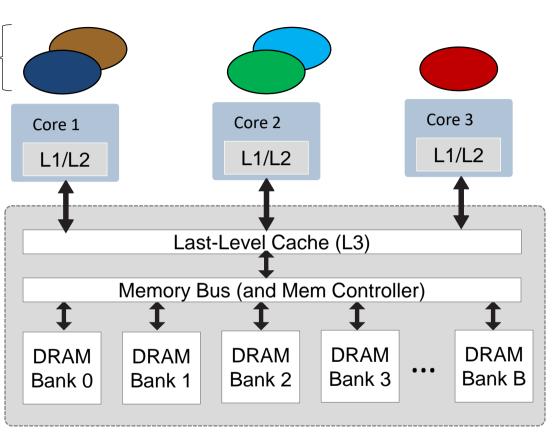

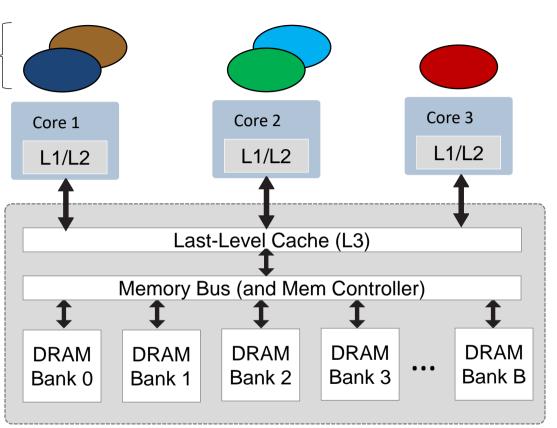

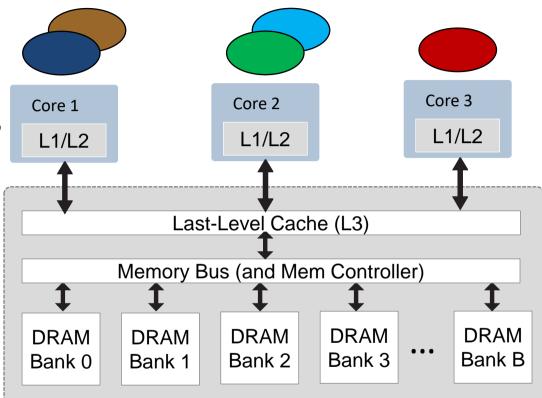

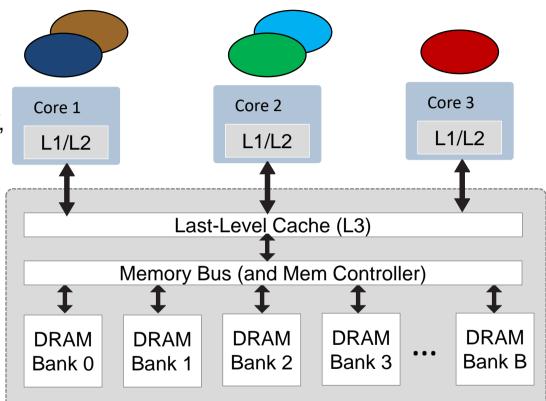

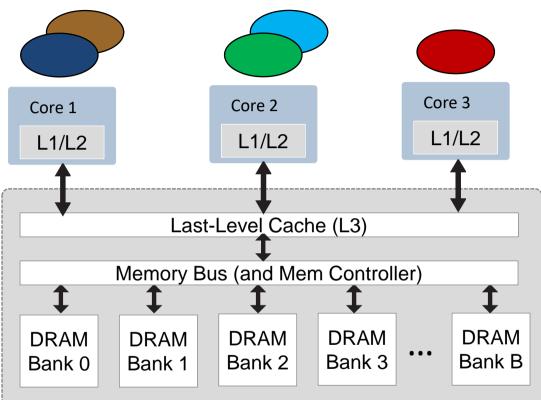

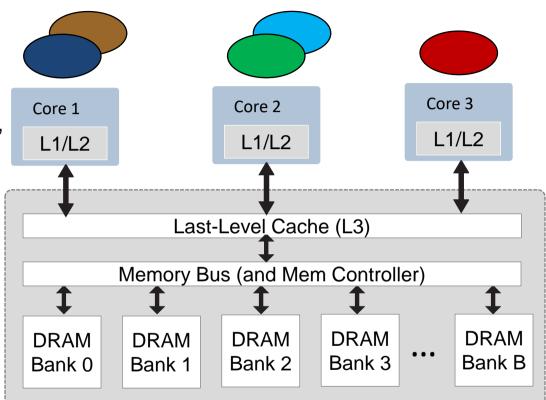

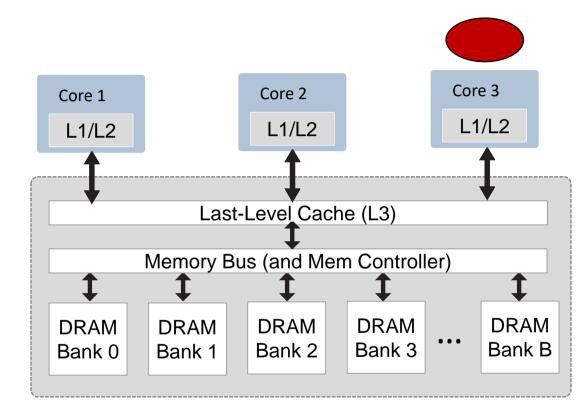

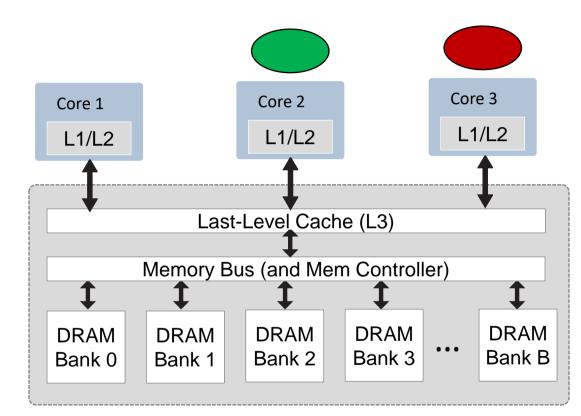

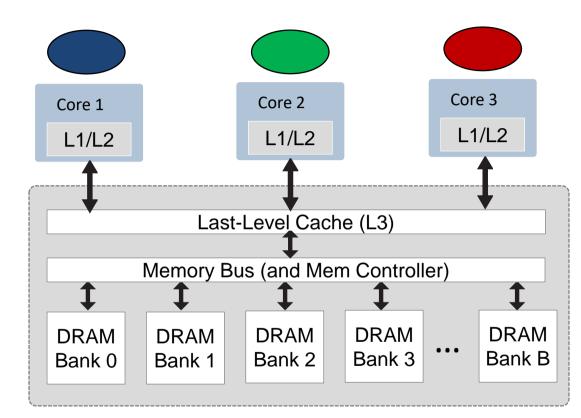

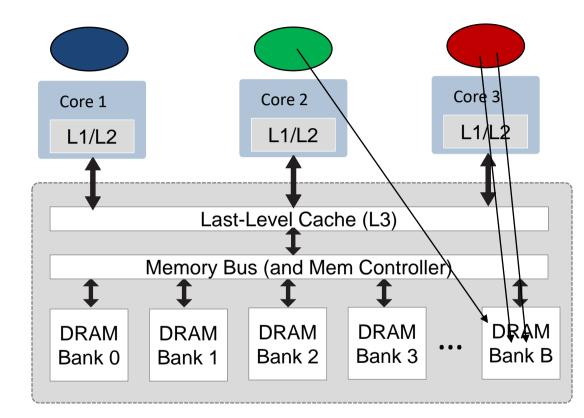

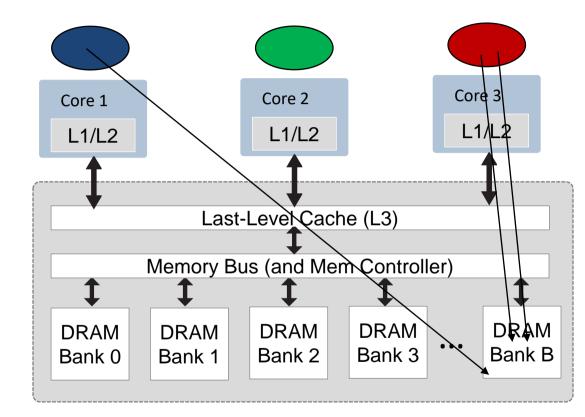

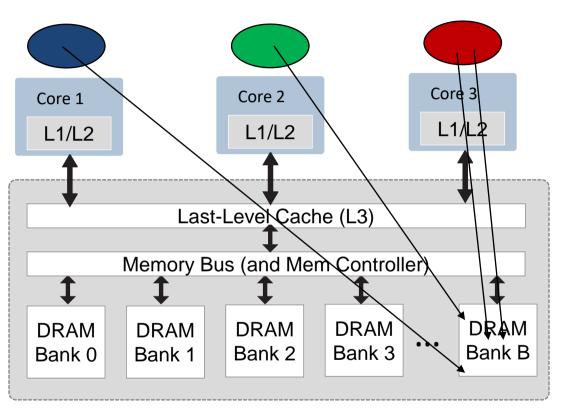

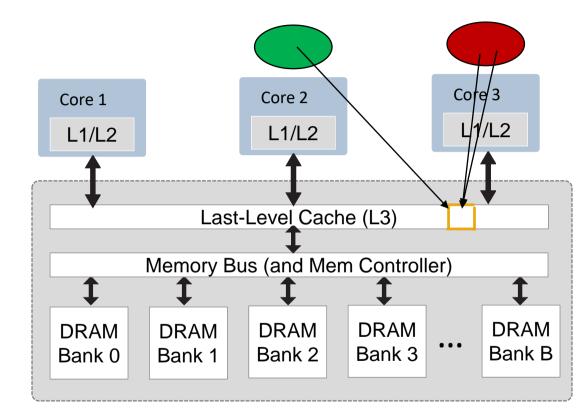

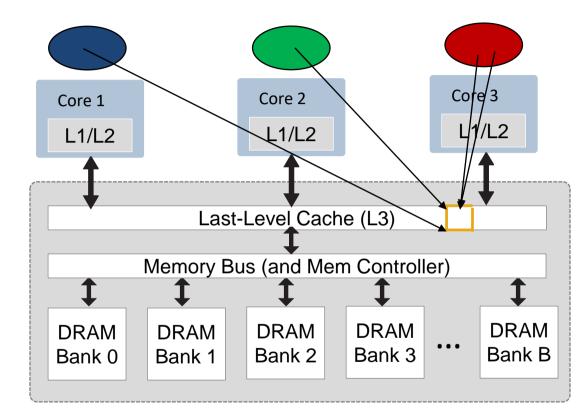

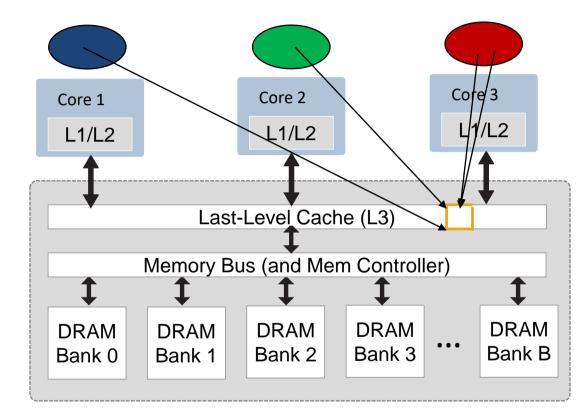

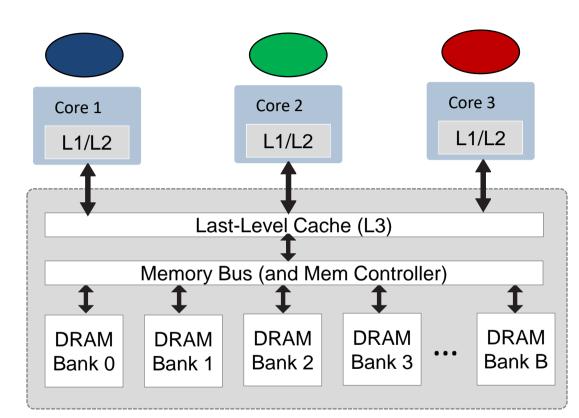

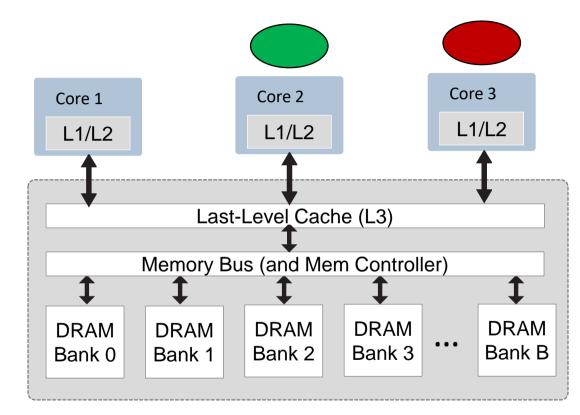

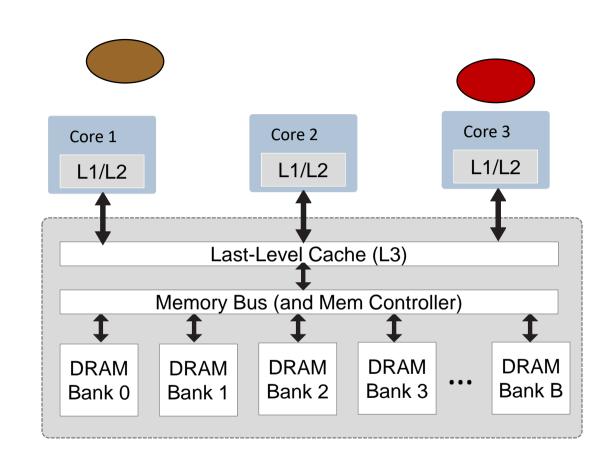

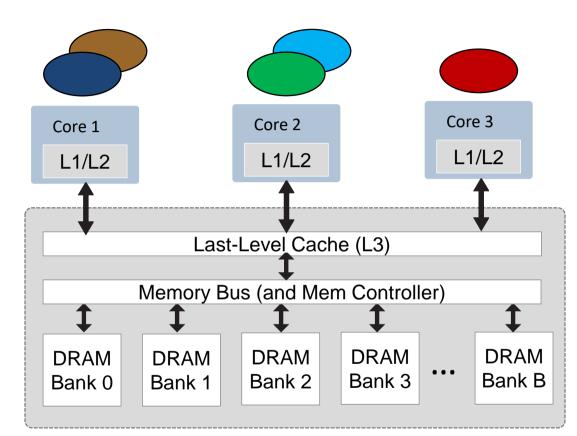

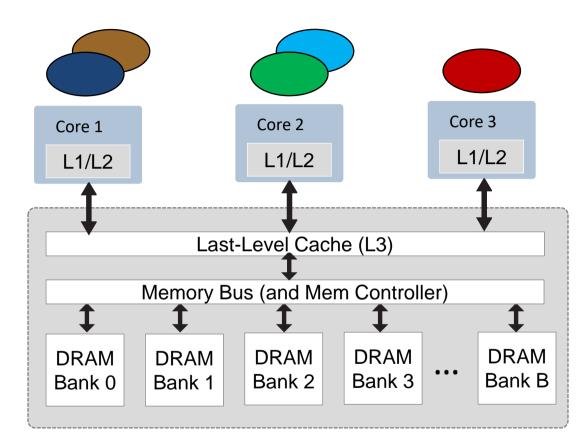

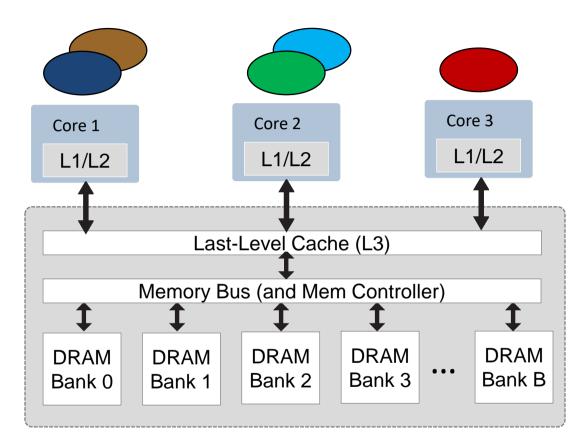

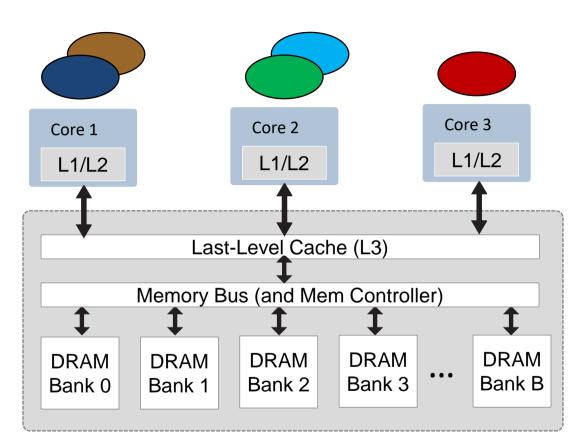

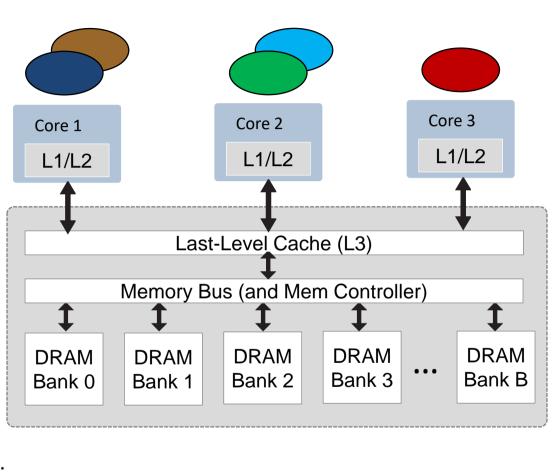

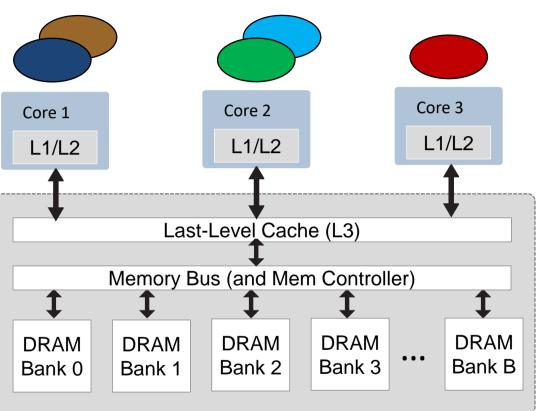

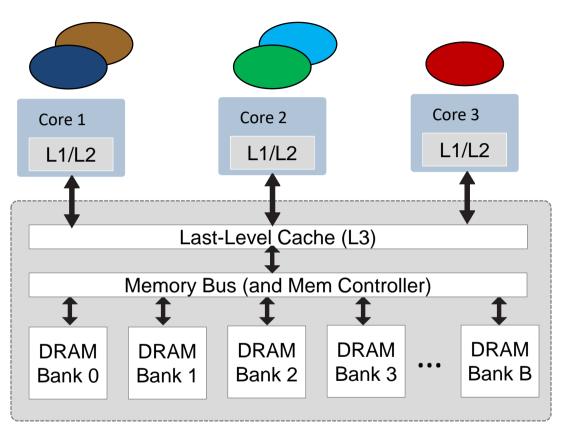

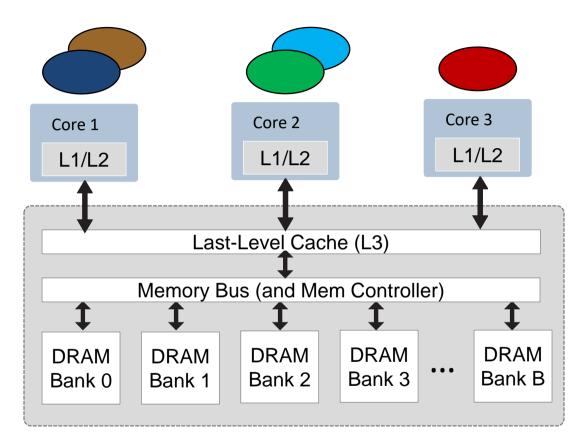

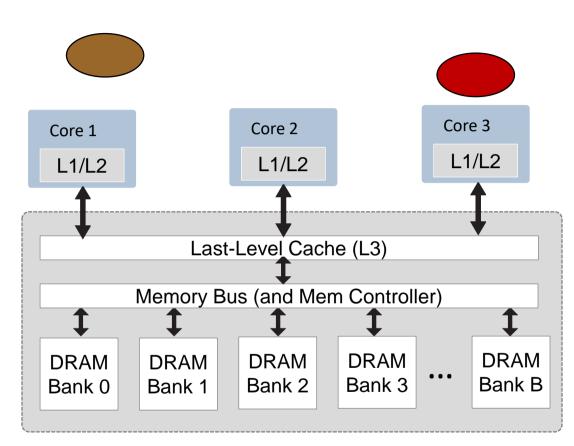

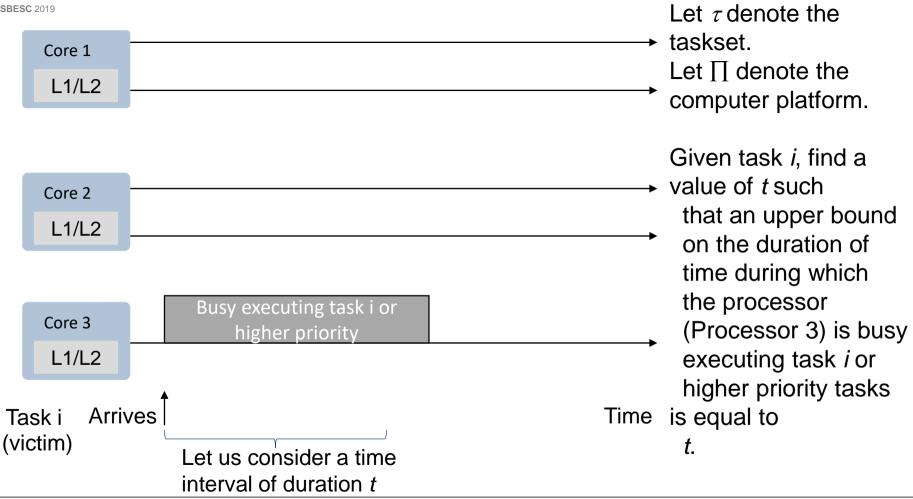

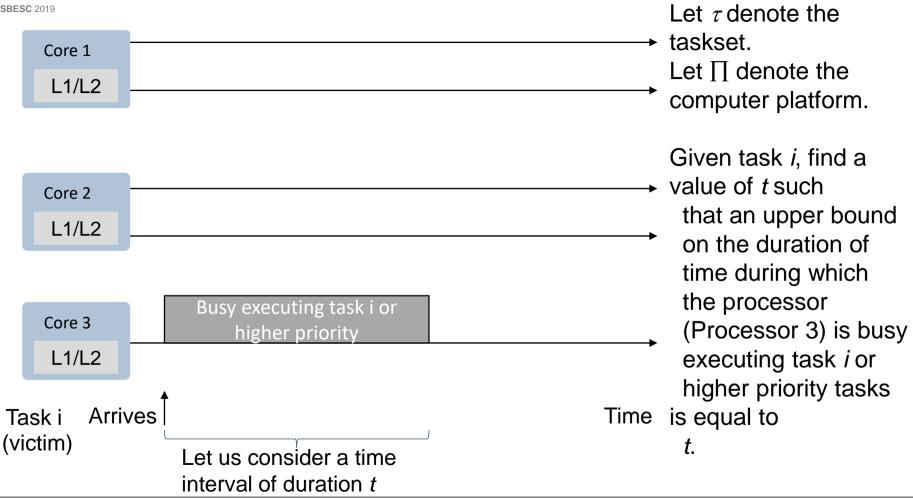

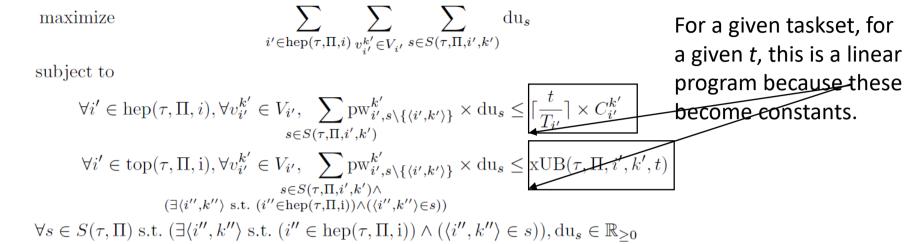

Core 1

L1/L2

Processes

\*H. Yun and P. K. Valsan, "Evaluating the Isolation Effect of Cache Partitioning on COTS Multicore Platforms," OSPERT, 2015. Core 2

L1/L2

Core 3

L1/L2

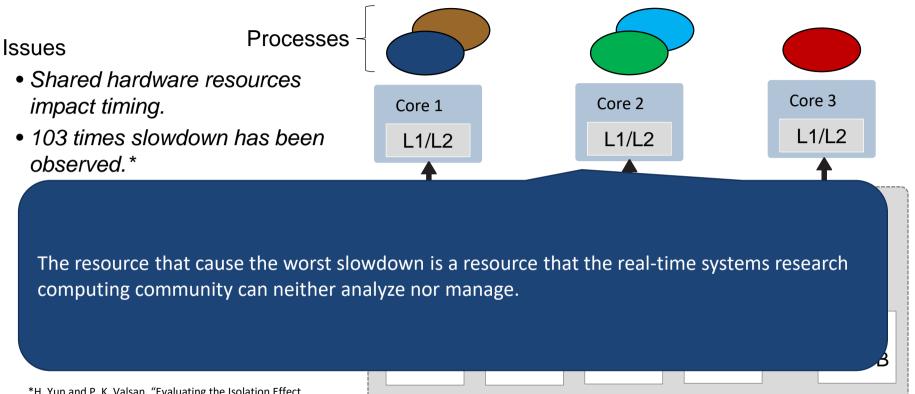

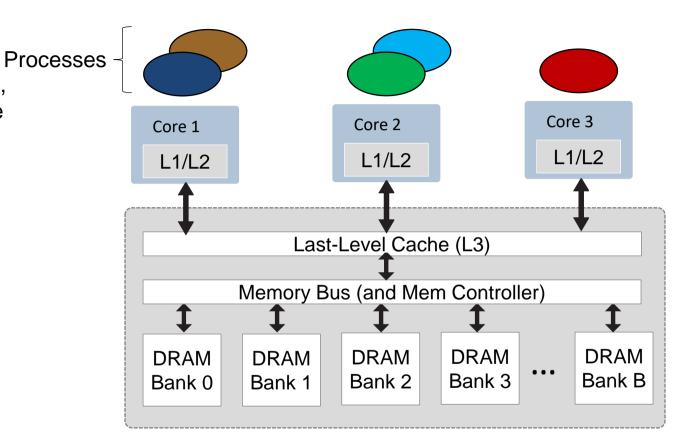

- Shared hardware resources impact timing.

- 103 times slowdown has been observed.\*

Processes

This slowdown is caused by Miss-Status Holding Register (MSHR). At that time, most researchers in real-time systems community were not aware of the MSHR. There was no schedulability analysis that incorporated MSHR.

Core 1

L1/L2

\*H. Yun and P. K. Valsan, "Evaluating the Isolation Effect of Cache Partitioning on COTS Multicore Platforms," OSPERT, 2015. Core 2

L1/L2

Core 3

L1/L2

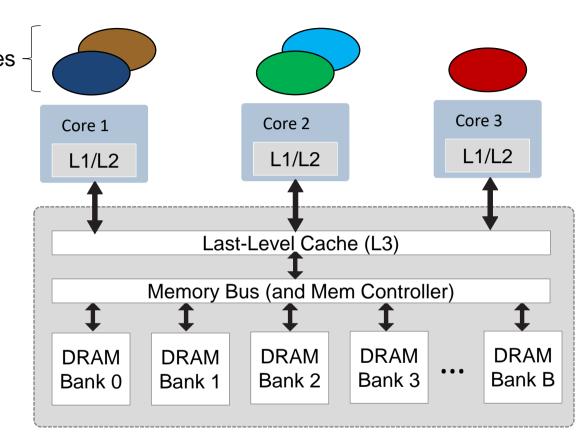

- Shared hardware resources impact timing.

- 103 times slowdown has been observed.\*

Processes

This slowdown is caused by Miss-Status Holding Register (MSHR). At that time, most researchers in real-time systems community were not aware of the MSHR. There was no schedulability analysis that incorporated MSHR. Even today, there is no schedulability analysis that incorporated MSHR.

Core 1

L1/L2

\*H. Yun and P. K. Valsan, "Evaluating the Isolation Effect of Cache Partitioning on COTS Multicore Platforms," OSPERT, 2015. Core 2

L1/L2

Core 3

L1/L2

\*H. Yun and P. K. Valsan, "Evaluating the Isolation Effect of Cache Partitioning on COTS Multicore Platforms," OSPERT, 2015.

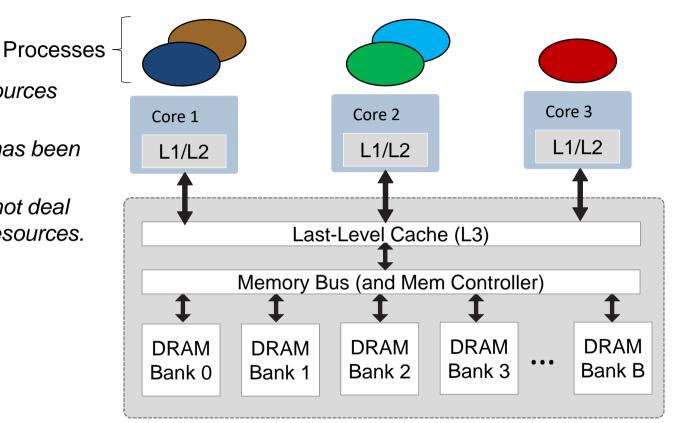

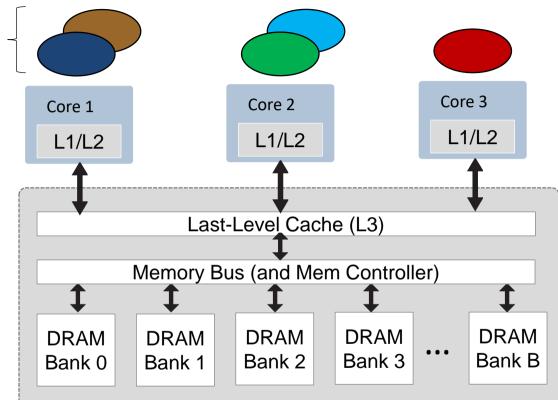

- Shared hardware resources impact timing.

- 103 times slowdown has been observed [Yun15].

- Current methods cannot deal with undocumented resources.

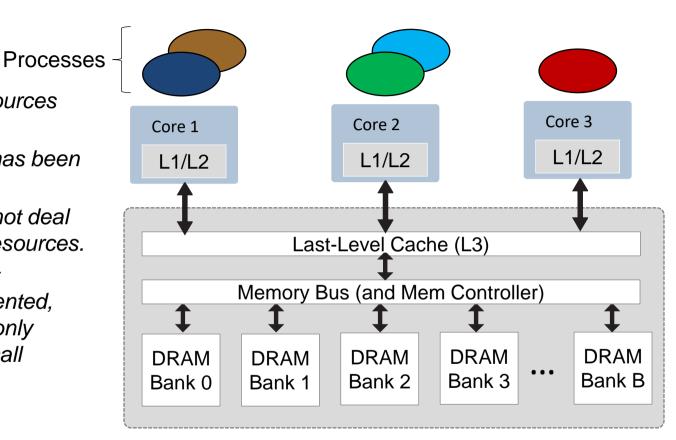

- Shared hardware resources impact timing.

- 103 times slowdown has been observed [Yun15].

- Current methods cannot deal with undocumented resources.

- Even for the case that resources are documented, current methods can only analyze/manage a small set of them.

- Shared hardware resources impact timing.

- 103 times slowdown has been observed [Yun15].

- Current methods cannot deal with undocumented resources.

- Even when resources are documented, current methods can only analyze/manage a small set of them.

- The problem is getting worse:

- \* Slowdown increasing

- \* More undocumented h/w

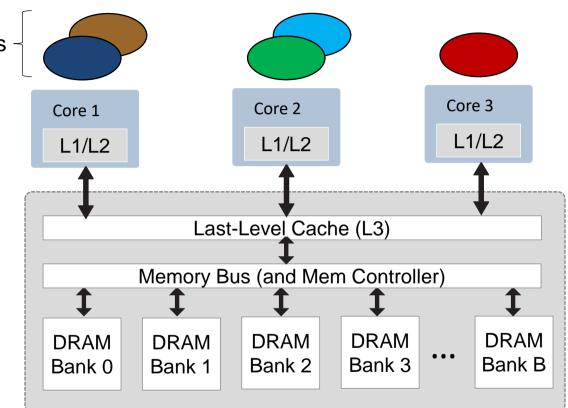

**Problem:** For each process, compute its response time

#### Processes - **Problem:** For each process, compute an upper bound on its response time

Processes -

**Problem:** For each process, compute an upper bound on its response time considering contention for resources in the memory system

#### and

that resources in the memory system are undocumented.

### Documented resources

DRAM memory timing tends to be specified according to JDEC standard.

#### **Documented resources**

DRAM memory timing tends to be specified according to JDEC standard.

### **Undocumented resources**

- Memory controller is often undocumented.

- Interconnection network from cores to Last-Level cache is often undocumented.

- Miss-Status Holding Register is often undocumented.

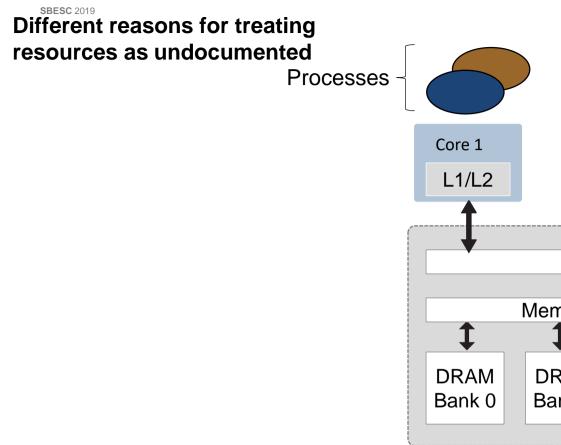

Resources are undocumented

- Resources are Processes undocumented

- Resources are documented but documentation is incorrect

- Resources are Processes undocumented

- Resources are documented but documentation is incorrect

- Heule:PLDI16:

50 out of 1795 x86

instructions have incorrect

documentation

- Resources are Processes undocumented

- Resources are documented but documentation is incorrect

- Heule:PLDI16: 50 out of 1795 x86 instructions have incorrect documentation

- Dasgupta:PLDI19: Found incorrect documentation of instructions for x86.

- Resources are Processes undocumented

- Resources are documented but documentation is incorrect

- Heule:PLDI16:

50 out of 1795 x86

instructions have incorrect

documentation

- Dasgupta:PLDI19: Found incorrect documentation of instructions for x86.

- Fog19:

There are discrepancies between measured latencies and latencies in data sheets.

- Resources are Processes undocumented

- Resources are documented but documentation is incorrect

- Resources are documented but one believes the documentation to be incorrect

- Resources are Processes undocumented

- Resources are documented but documentation is incorrect

- Resources are documented but one believes the documentation to be incorrect

- Resources are documented and one believe documentation to be correct but it is laborious to create a timing model for schedulability analysis

- Resources are Processes

undocumented

- Resources are documented but documentation is incorrect

- Resources are documented but one believes the documentation to be incorrect

- Resources are documented and one believe documentation to be correct but it is laborious to create a timing model for schedulability analysis (and it needs to be changed when one buys a new chip anyway)

#### **SBESC** 2019

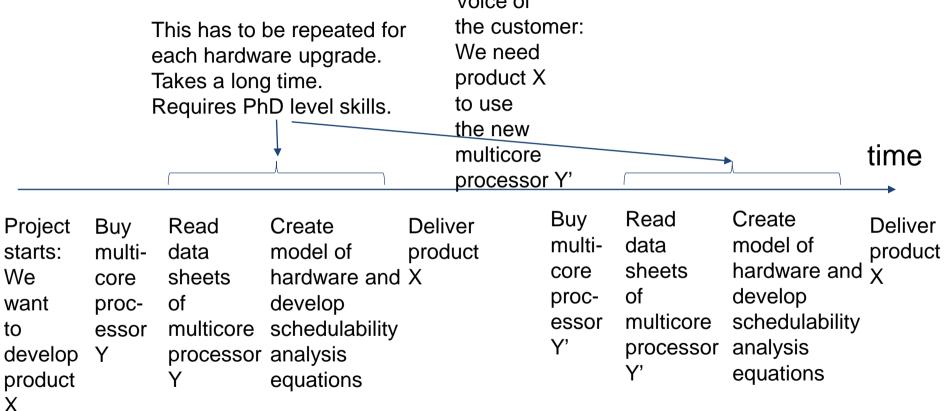

The consequences of analyzing timing of software executing on multicores using documentation

#### SBESC 2019

The consequences of analyzing timing of software executing on multicores using documentation

### time

## The consequences of analyzing timing of software executing on multicores using documentation

### time

| Project |

|---------|

| starts: |

| We      |

| want    |

| to      |

| develop |

| product |

| Х       |

#### time

| Project | Buy    |

|---------|--------|

| starts: | multi- |

We core

want proc-

to essor

develop Y

product

Х

#### time

| Project<br>starts:<br>We | Buy<br>multi-<br>core | Read<br>data<br>sheets |

|--------------------------|-----------------------|------------------------|

| want<br>to               | proc-                 | of<br>multicore        |

|                          | essor                 |                        |

| develop                  | Y                     | processor              |

| product                  |                       | Y                      |

| Х                        |                       |                        |

### time

| Project | Buy    | Read      | Create         |

|---------|--------|-----------|----------------|

| starts: | multi- | data      | model of       |

| We      | core   | sheets    | hardware and   |

| want    | proc-  | of        | develop        |

| to      | essor  | multicore | schedulability |

| develop | Y      | processor | analysis       |

| product |        | Υ         | equations      |

| Х       |        |           |                |

### time

| Project | Buy    | Read      | Create         | Deliver |

|---------|--------|-----------|----------------|---------|

| starts: | multi- | data      | model of       | product |

| We      | core   | sheets    | hardware and   | Х       |

| want    | proc-  | of        | develop        |         |

| to      | essor  | multicore | schedulability |         |

| develop | Y      | processor | analysis       |         |

| product |        | Υ         | equations      |         |

| Х       |        |           |                |         |

#### The consequences of analyzing timing of software executing on multicores using documentation Voice of the customer: We need product X to use the new multicore processor Y'

| Project<br>starts:<br>We<br>want | Buy<br>multi-<br>core<br>proc- | Read<br>data<br>sheets<br>of | Create<br>model of<br>hardware and<br>develop | Deliver<br>product<br>X |

|----------------------------------|--------------------------------|------------------------------|-----------------------------------------------|-------------------------|

| to<br>develop<br>product<br>X    | essor<br>Y                     | multicore<br>processor<br>Y  | schedulability<br>analysis<br>equations       |                         |

#### SBESC 2019 The consequences of analyzing timing of software executing on multicores using documentation Voice of the customer: We need product X to use the new multicore time processor Y' Buv Read Create Deliver Project Create Deliver Buy Read model of multidata product product starts: data model of multihardware and $\chi$ sheets core We hardware and X sheets core of develop procof want develop procschedulability multicore essor multicore schedulability to essor Y' analysis processor develop analysis Y processor Y' equations product Y equations Х

**SBESC** 2019

| New multicore |

|---------------|

| processor Y   |

| becomes       |

| available     |

time

| New multicore |      |

|---------------|------|

| processor Y   |      |

| becomes       | time |

| available     |      |

|               |      |

Academic researcher create model of hardware and develop schedulability analysis equations for Y

| New multico<br>processor Y<br>becomes<br>available |                                                                                                                        | New multicore<br>processor Y'<br>becomes<br>available | time |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------|

|                                                    | Academic<br>researcher<br>create<br>model of<br>hardware and<br>develop<br>schedulability<br>analysis<br>equations for |                                                       |      |

| New multicore<br>processor Y<br>becomes<br>available | New multico<br>processor Y<br>becomes<br>available |                                                                                                                           | time |

|------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|

| rese<br>creat<br>mod<br>hard<br>deve<br>sche<br>anal | el of<br>ware and<br>elop<br>edulability           | Academic<br>researcher<br>create<br>model of<br>hardware and<br>develop<br>schedulability<br>analysis<br>equations for Y' |      |

| New multico<br>processor Y<br>becomes<br>available |                                                                                                                     | New multicor<br>processor Y'<br>becomes<br>available |                                                                                                                     | New multicore<br>processor Y"<br>becomes<br>available | time |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------|

|                                                    | Academic<br>researcher<br>create<br>model of<br>hardware an<br>develop<br>schedulabilit<br>analysis<br>equations fo | y                                                    | Academic<br>researcher<br>create<br>model of<br>hardware an<br>develop<br>schedulabilit<br>analysis<br>equations fo | ty                                                    |      |

| New multicore<br>processor Y<br>becomes<br>available | New multice<br>processor N<br>becomes<br>available                                                                  |                                                                                                                    | New multico<br>processor Y'<br>becomes<br>available | -                                                                                                                         | time |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|

| re<br>cr<br>m<br>ha<br>de<br>so<br>ai                | Academic<br>esearcher<br>reate<br>nodel of<br>ardware and<br>levelop<br>chedulability<br>nalysis<br>equations for Y | Academic<br>researcher<br>create<br>model of<br>hardware ar<br>develop<br>schedulabili<br>analysis<br>equations fo | ty                                                  | Academic<br>researcher<br>create<br>model of<br>hardware and<br>develop<br>schedulability<br>analysis<br>equations for Y" |      |

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

Treating multicore processors as undocumented hardware has the potential to create a model that can be used for processors in the future even for processors that we currently do not know about.

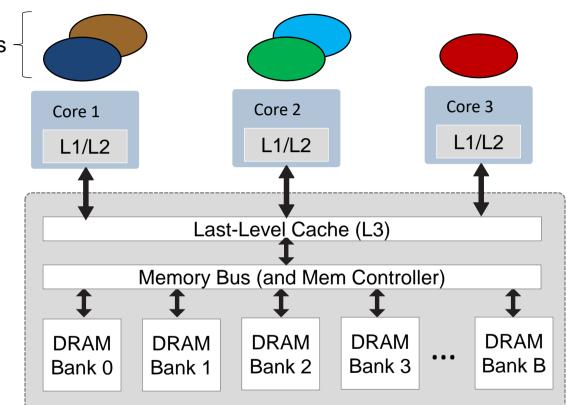

**Problem:** For each process, compute its response time

#### Processes - **Problem:** For each process, compute an upper bound on its response time

**Problem:** For each process, compute an upper bound on its response time considering contention for resources in the memory system

#### and

that resources in the memory system are undocumented.

**Problem:** For each process, compute an upper bound on its response time considering contention for resources in the memory system

and

that resources in the memory system are undocumented.

**Q:** How can we analyze timing of a system when we do not know how the system works?

**Problem:** For each process, compute an upper bound on its response time considering contention for resources in the memory system

and

that resources in the memory system are undocumented.

**Q:** How can we analyze timing of a system when we do not know how the system works?

A: Create abstraction that describes effect of undocumented h/w.

#### **Big Research Questions**

#### **Big Research Questions**

**Q1:** What is a good abstraction that describes the effect of undocumented hardware?

**Q2:** How to create a schedulability analysis that uses this abstraction?

#### **Big Research Questions**

**Q1:** What is a good abstraction that describes the effect of undocumented hardware?

**Q2:** How to create a schedulability analysis that uses this abstraction?

Before discussing them, let us discuss:

- 1. Other approaches

- 2. General ideas for abstractions in other disciplines

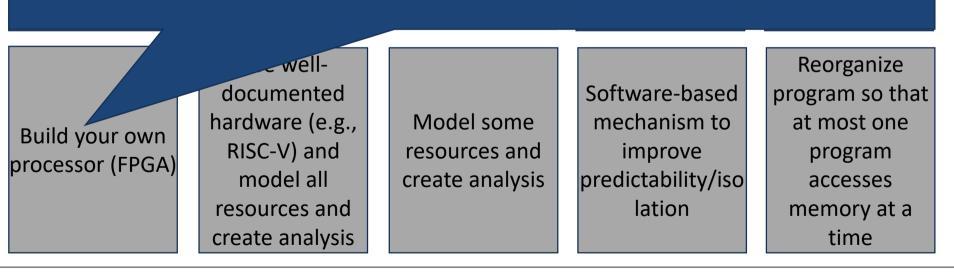

Ignore timing requirements

Ignore timing requirements

Ignore timing aspects of memory system

Ignore timing requirements

Ignore timing aspects of memory system Disable all processor cores except one

Ignore timing requirements

Ignore timing aspects of memory system Disable all processor cores except one Use simple processor and run heavy computations on GPU

Ignore timing requirements

Ignore timing aspects of memory system Disable all processor cores except one Use simple processor and run heavy computations on GPU

Build your own processor (ASIC)

Ignore timing requirements

Ignore timing aspects of memory system Disable all processor cores except one Use simple processor and run heavy computations on GPU

Build your own processor (ASIC)

Build your own processor (FPGA)

> **Carnegie Mellon University** Software Engineering Institute

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release and unlimited distribution.

Ignore timing requirements

Ignore timing aspects of memory system Disable all processor cores except one Use simple processor and run heavy computations on GPU

Build your own processor (ASIC)

Build your own processor (FPGA) Use welldocumented hardware (e.g., RISC-V) and model all resources and create analysis

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release and unlimited distribution.

| Ignore timing<br>requirements     | Ignore timing<br>aspects of<br>memory system                                            | Disable all<br>processor cores<br>except one   |

|-----------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------|

| Build your own<br>rocessor (FPGA) | Use well-<br>documented<br>hardware (e.g.,<br>RISC-V) and<br>model all<br>resources and | Model some<br>resources and<br>create analysis |

create analysis

Use simple processor and run heavy computations on GPU

Build your own processor (ASIC)

**Carnegie Mellon University** Software Engineering Institute

p

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

| Ignore timing<br>requirements      | Ignore timing<br>aspects of<br>memory system                                                               | Disable all<br>processor cores<br>except one   | Use simple<br>processor and<br>run heavy<br>computations on<br>GPU        | Build your own<br>processor (ASIC) |  |  |

|------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------|------------------------------------|--|--|

| Build your own<br>processor (FPGA) | Use well-<br>documented<br>hardware (e.g.,<br>RISC-V) and<br>model all<br>resources and<br>create analysis | Model some<br>resources and<br>create analysis | Software-based<br>mechanism to<br>improve<br>predictability/iso<br>lation |                                    |  |  |

**Carnegie Mellon University** Software Engineering Institute

| Ignore timing<br>requirements      | Ignore timing<br>aspects of<br>memory system                                                               | Disable all<br>processor cores<br>except one   | Use simple<br>processor and<br>run heavy<br>computations on<br>GPU        | Build your own<br>processor (ASIC)                                                         |

|------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Build your own<br>processor (FPGA) | Use well-<br>documented<br>hardware (e.g.,<br>RISC-V) and<br>model all<br>resources and<br>create analysis | Model some<br>resources and<br>create analysis | Software-based<br>mechanism to<br>improve<br>predictability/iso<br>lation | Reorganize<br>program so that<br>at most one<br>program<br>accesses<br>memory at a<br>time |

Ignore timing requirements

#### Ignore timing aspects of memory system

Disable all processor cores except one Use simple processor and run heavy computations on GPU

Build your own processor (ASIC)

#### **Pro:** Easy **Con**: Potentially unsafe

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release and unlimited distribution.

Ignore timing requirements

Ignore timing aspects of memory system Disable all processor cores except one Use simple processor and run heavy computations on GPU

Build your own processor (ASIC)

#### **Pro:** Easy **Con:** Potentially unsafe

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release and unlimited distribution.

Ignore timing requirements Ignore timing aspects of memory system Disable all processor cores except one Use simple processor and run heavy computations on GPU

Build your own processor (ASIC)

## Pro: Easy Con: Lose lots of processing capacity

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

Ignore timing requirements

Ignore timing aspects of memory system Disable all processor cores except one Use simple processor and run heavy computations on GPU

Build your own processor (ASIC)

## **Con:** Analyzing timing of a single "task" executing on a GPU is still hard.

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

Ignore timing requirements

Ignore timing aspects of memory system Disable all processor cores except one Use simple processor and run heavy computations on GPU

Build your own processor (ASIC)

## Con: High fixed cost.

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

## **Con:** Low clock frequency

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

### **Con:** Limits #suppliers. Laborious.

|                                    |  | Use well-       |                 |                    | Reorganize      |

|------------------------------------|--|-----------------|-----------------|--------------------|-----------------|

| Build your own<br>processor (FPGA) |  | documented      |                 | Software-based     | program so that |

|                                    |  | hardware (e.g., | Model some      | mechanism to       | at most one     |

|                                    |  | RISC-V) and     | resources and   | improve            | program         |

|                                    |  | model all       | create analysis | predictability/iso | accesses        |

|                                    |  | resources and   |                 | lation             | memory at a     |

|                                    |  | create analysis |                 |                    | time            |

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

### **Con:** Laborious. There may be many resources for which documentation does not exist.

| Build your own<br>processor (FPGA) |

|------------------------------------|

| processor (FPGA)                   |

Use welldocumented hardware (e.g., RISC-V) and model all resources and create analysis

Model some resources and create analysis Software-based mechanism to improve predictability/iso lation Reorganize program so that at most one program accesses memory at a time

**Carnegie Mellon University** Software Engineering Institute

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

Examples: Cache coloring, Cache locking, Bank coloring, MemGuard, TLB coloring.Con: Requires changes to operating system. Only work for some resources; there are many resources for which there is no isolation mechanism.

| Build your own<br>processor (FPGA) | Use well-<br>documented<br>hardware (e.g.,<br>RISC-V) and<br>model all<br>resources and<br>create analysis | Model some<br>resources and<br>create analysis | Software-based<br>mechanism to<br>improve<br>predictability/iso<br>lation | Reorganize<br>program so that<br>at most one<br>program<br>accesses<br>memory at a<br>time |

|------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

|------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

### **Examples:** PREM, Linkoping@RTSS07.

**Con:** Laborious. Requires a local memory that is large enough to store working set. Difficult to prove that no memory accesses occurs in certain phases.

| Build your own<br>processor (FPGA) | Use well-<br>documented<br>hardware (e.g.,<br>RISC-V) and<br>model all<br>resources and<br>create analysis | Model some<br>resources and<br>create analysis | Software-based<br>mechanism to<br>improve<br>predictability/iso<br>lation | Reorganize<br>program so that<br>at most one<br>program<br>accesses<br>memory at a<br>time |

|------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

|------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

Processes -

## **Big Research Questions**

**Q1:** What is a good abstraction that describes the effect of undocumented hardware?

**Q2:** How to create a schedulability analysis that uses this abstraction?

Before discussing them, let us discuss:

- 1. Other approaches (DONE)

- 2. General ideas for abstractions in other disciplines

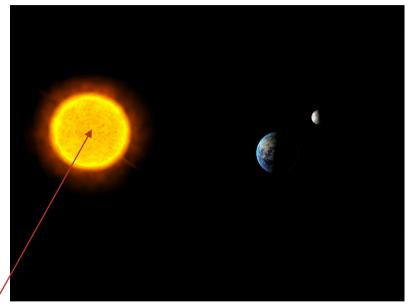

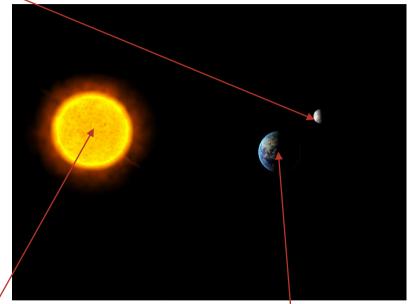

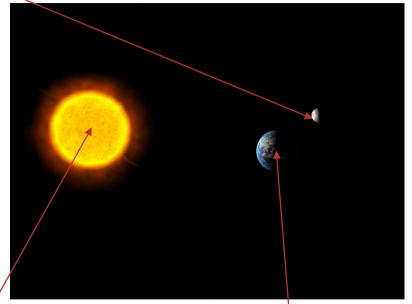

### Not drawn to scale

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

## This body has many atoms

**Carnegie Mellon University** Software Engineering Institute

# General ideas for abstractions in other disciplines

## This body has many atoms This body has many atoms

**Carnegie Mellon University** Software Engineering Institute

# General ideas for abstractions in other disciplines

## This body also has many atoms

## This body has many atoms This body has many atoms

**Carnegie Mellon University** Software Engineering Institute

# General ideas for abstractions in other disciplines

## This body also has many atoms

## We describe each body as a single point mass

## This body has many atoms This body has many atoms

**Carnegie Mellon University** Software Engineering Institute

# General ideas for abstractions in other disciplines

## This body also has many atoms

## We describe each body as a single point mass

## This body has many atoms This body has many atoms

# Describe each body with only as many parameters that we need for the analysis that we want to do.

**Carnegie Mellon University** Software Engineering Institute

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

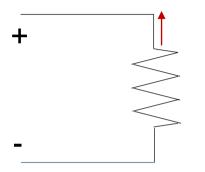

# General ideas for abstractions in other disciplines

How many electrons per time unit are flowing here?

# General ideas for abstractions in other disciplines

How much current is flowing here?

# General ideas for abstractions in other disciplines

How much current is flowing here?

## Ask questions about the aggregate that you care about.

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

For **each** of these 10<sup>24</sup> water molecules, how fast does this water molecule move?

**Carnegie Mellon University** Software Engineering Institute

SBESC 2019

# General ideas for abstractions in other disciplines

What is the water temperature?

## Ask questions about the aggregate that you care about.

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

# General ideas for abstractions in other disciplines

What is the water temperature?

# If possible: Describe a system with quantities that you can measure.

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

# General ideas for abstractions in other disciplines

1. Describe a system with parts

2. Describe each part with an abstraction

3. Obtain specific values of the abstraction (e.g., using measurements) for each part

## 4. Ask questions: calculate the answer to the questions

# General ideas for abstractions

1. Describe a system with parts

2. Describe each part with an abstraction

3. Obtain specific values of the abstraction (e.g., using measurements) for each part

## 4. Ask questions: calculate the answer to the questions

# General ideas for abstractions

- Describe a system with parts

A software system comprises a set of tasks.

- Describe each part with an abstraction Each task is described with a T (period), D (deadline), and C (execution time).

- Obtain specific values of the abstraction (e.g., using measurements) for each part Obtain T from source code. Obtain D from software requirement specification. Obtain C by measuring the execution of the program; then add margin. (or run WCET tool)

4. Ask questions: calculate the answer to the questions Will all deadlines be met if tasks are scheduled by Rate-Monotonic on a single processor?

# General ideas for abstractions

- Describe a system with parts

A software system comprises a set of tasks.

- Describe each part with an abstraction Each task is described with a T (period), D (deadline), and C (execution time). Describe the effect of the memory system on execution speed of a task.

- Obtain specific values of the abstraction (e.g., using measurements) for each part Obtain T from source code. Obtain D from software requirement specification. Obtain C by measuring the execution of the program; then add margin. (or run WCET tool) Obtain parameters (e.g., using measurements)

- 4. Ask questions: calculate the answer to the questions Will all deadlines be met if tasks are scheduled by Rate-Monotonic on a single processor?

## **Big Research Questions**

**Q1:** What is a good abstraction that describes the effect of undocumented hardware?

**Q2:** How to create a schedulability analysis that uses this abstraction?

Before discussing them, let us discuss:

- 1. Other approaches (DONE)

- 2. General ideas for abstractions in other disciplines (DONE)

## **Big Research Questions**

Q1: What is a good abstraction that describes the effect of undocumented hardware?

**Q2:** How to create a schedulability analysis that uses this abstraction?

Let us discuss Q1.

## **Big Research Questions**

**Q1:** What is a good abstraction that describes the effect of undocumented hardware?

**Q2:** How to create a schedulability analysis that uses this abstraction?

What are the requirements of a good abstraction?

## **Big Research Questions**

**Q1:** What is a good abstraction that describes the effect of undocumented hardware?

**Q2:** How to create a schedulability analysis that uses this abstraction?

- What are the requirements of a good abstraction?

- 1. It should be as small as possible (few numbers; few bits)

## **Big Research Questions**

**Q1:** What is a good abstraction that describes the effect of undocumented hardware?

**Q2:** How to create a schedulability analysis that uses this abstraction?

- What are the requirements of a good abstraction?

- 1. It should be as small as possible (few numbers; few bits)

- 2. It should allow us to do prediction/ analysis that we care about

## **Big Research Questions**

**Q1:** What is a good abstraction that describes the effect of undocumented hardware?

**Q2:** How to create a schedulability analysis that uses this abstraction?

- What are the requirements of a good abstraction?

- 1. It should be as small as possible (few numbers; few bits)

- 2. It should allow us to do prediction/ analysis that we care about

- 3. Given a system, it should be possible to find the abstraction (through measurements or lower-level analysis)

# Considerations in creating an abstraction for multicore

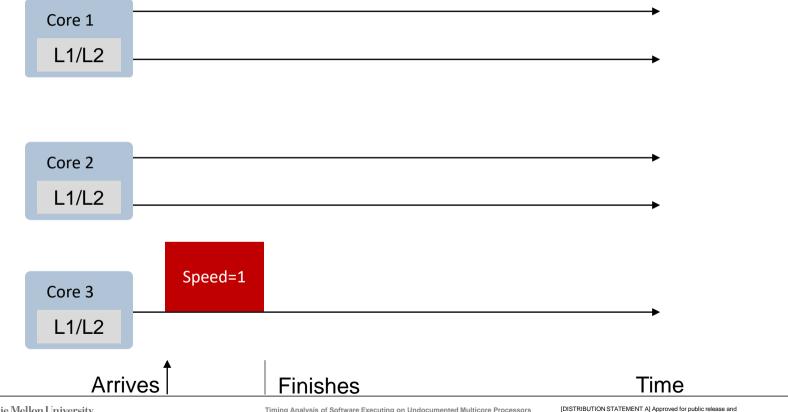

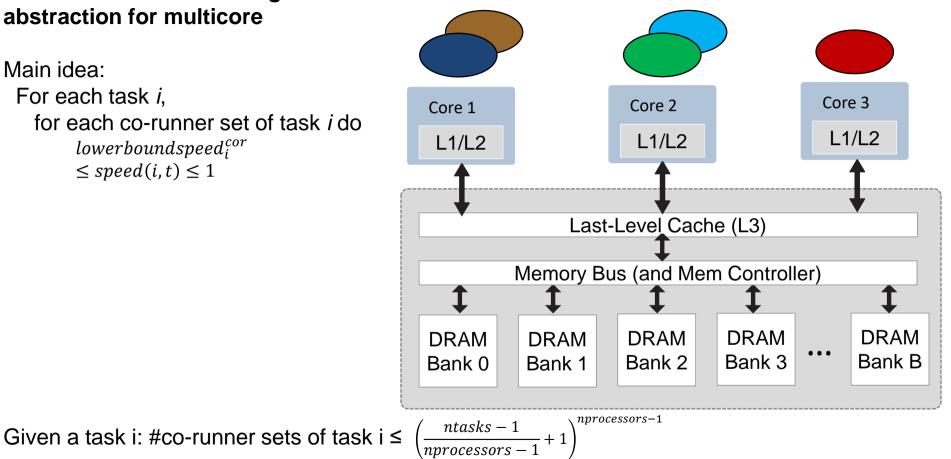

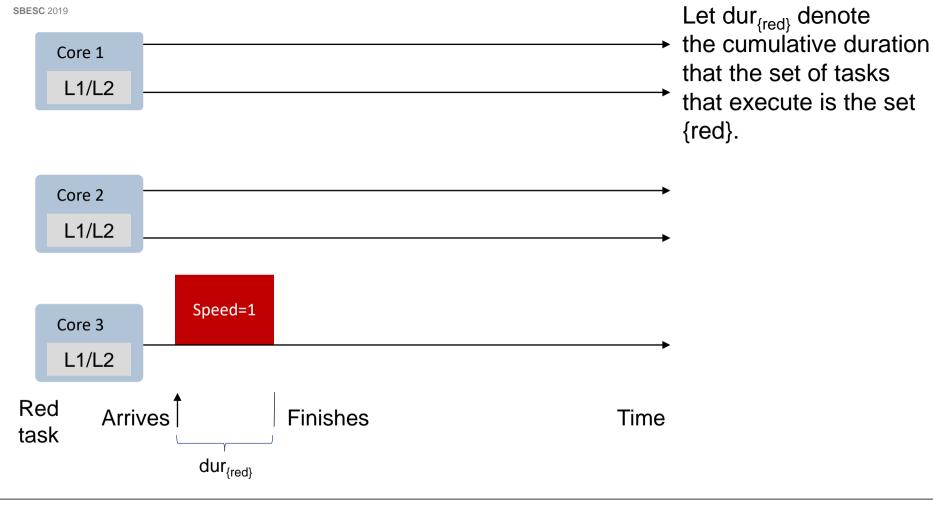

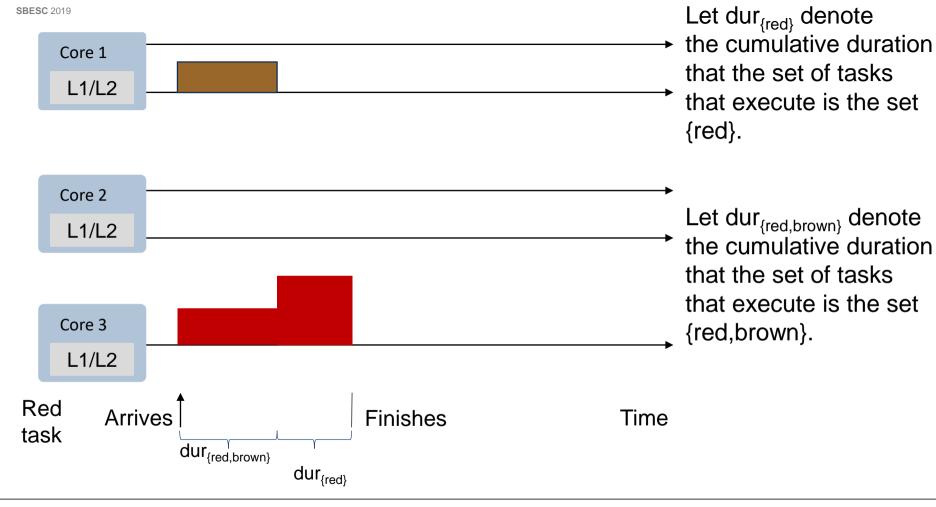

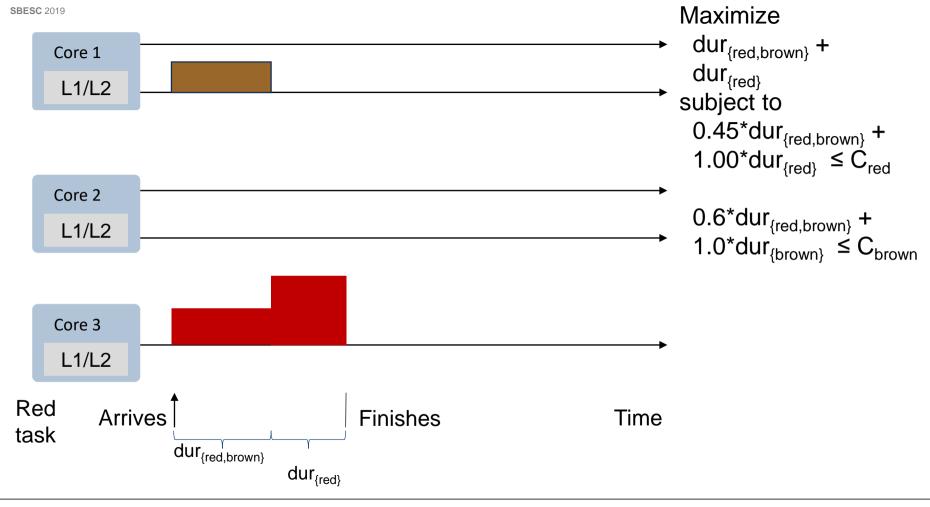

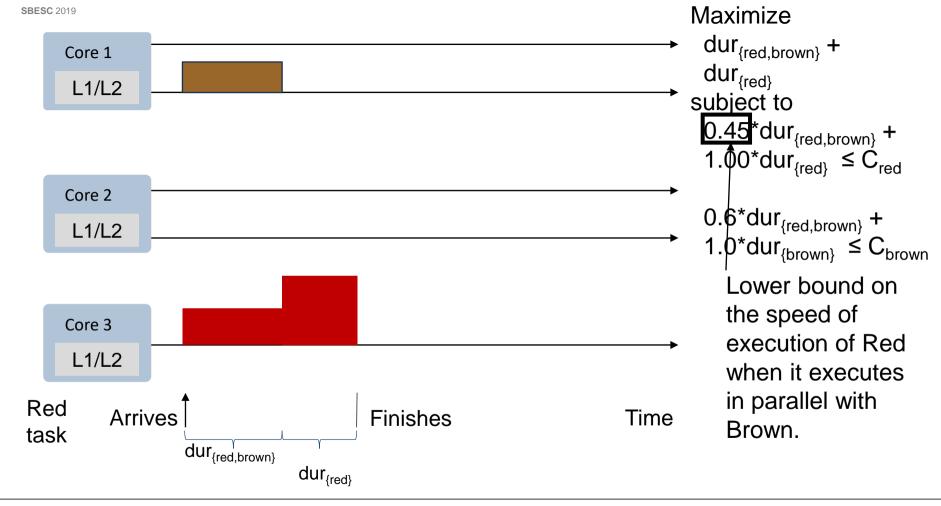

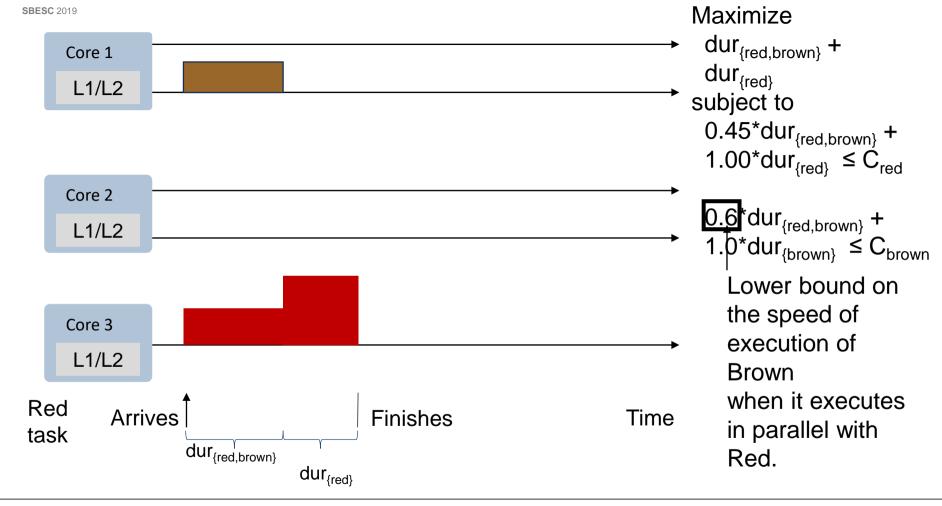

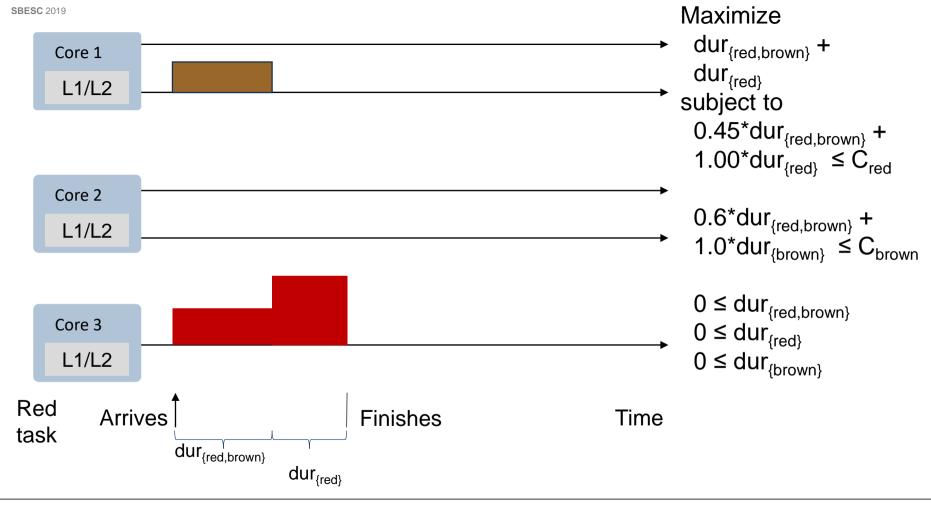

Let speed(i,t) denote the speed of execution of task *i* at time *t*. Let cor(i,t)denote the set of tasks, other than task *i*, that executes at time *t*.

### **SBESC** 2019 Considerations in creating an abstraction for multicore

Let *speed*(*i*,*t*) denote the speed of execution of task *i* at time *t*. Let cor(i,t)denote the set of tasks, other than task *i*. that executes at time t.

One abstraction could be:

$$\frac{1}{+|cor(i,t)|} \le speed(i,t) \le$$

Let speed(i,t) denote the speed of execution of task *i* at time *t*. Let cor(i,t)denote the set of tasks, other than task *i*, that executes at time *t*.

One abstraction could be:

$\frac{1}{1 + |cor(i,t)|} \le speed(i,t) \le 1$

Drawback of abstraction:

- Does not reflect that different corunners can have different effect on task *i*.

Let speed(i,t) denote the speed of execution of task *i* at time *t*. Let cor(i,t)denote the set of tasks, other than task *i*, that executes at time *t*.

One abstraction could be:

$1 - k \times |cor(i, t)| \leq speed(i, t) \leq 1$

Drawback of abstraction:

- Does not reflect that different corunners can have different effect on task *i*.

Let speed(i,t) denote the speed of execution of task *i* at time *t*. Let cor(i,t)denote the set of tasks, other than task *i*, that executes at time *t*.

One abstraction could be:

$$\frac{w_i}{1 + \sum_{j \mid j \in cor(i,t)} w_{i,j}} \le speed(i,t) \le 1$$

Drawback of abstraction:

In reality, the speed can be super -additive or sub-additive (not reflected in the above).

Let speed(i,t) denote the speed of execution of task *i* at time *t*. Let cor(i,t)denote the set of tasks, other than task *i*, that executes at time *t*.

One abstraction could be:

$\frac{w_i}{1 + \prod_{i \mid i \in cor(i,t)} w_{i,j}} \le speed(i,t) \le 1$

Drawback of abstraction:

In reality, the speed can be super -additive or sub-additive (not reflected in the above).

Let speed(i,t) denote the speed of execution of task *i* at time *t*. Let cor(i,t)denote the set of tasks, other than task *i*, that executes at time *t*.

One abstraction could be:

$\frac{w_i}{1 + e^{\sum_{j \mid j \in cor(i,t)} w_{i,j}}} \le speed(i,t) \le 1$

Drawback of abstraction:

In reality, the speed can be super -additive or sub-additive (not reflected in the above).

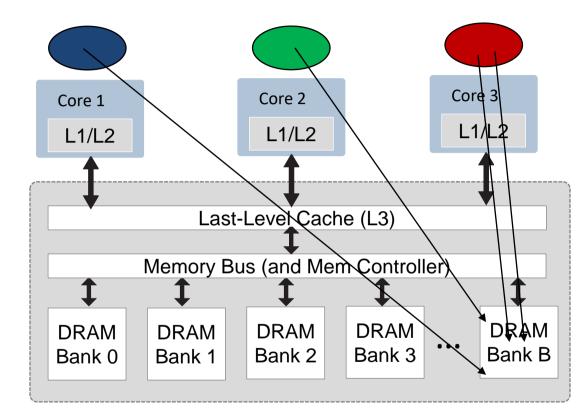

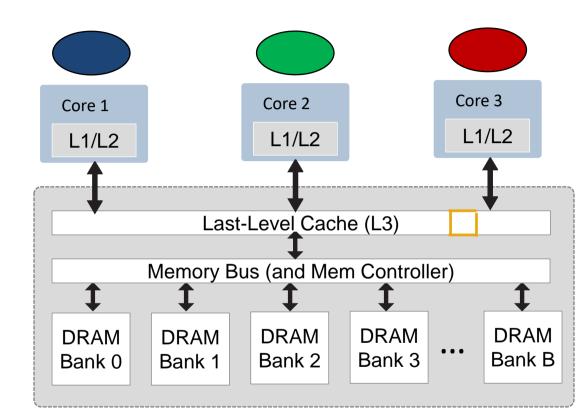

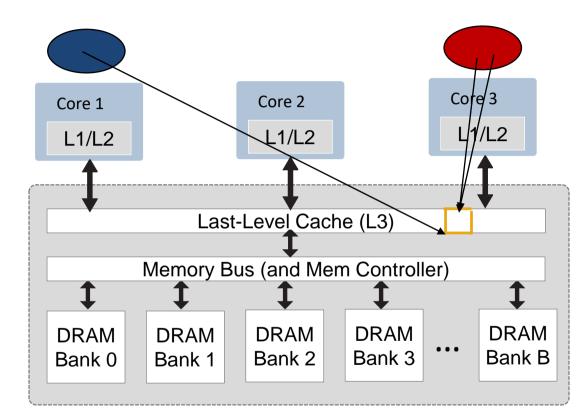

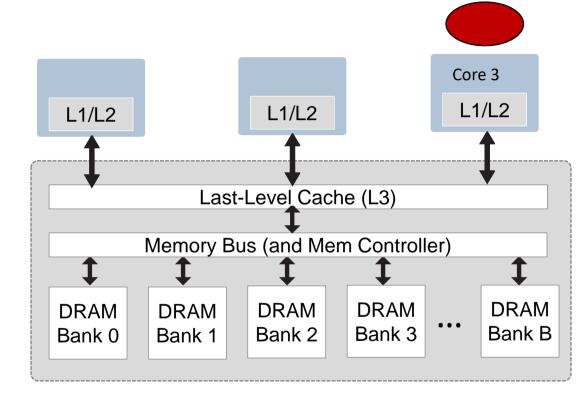

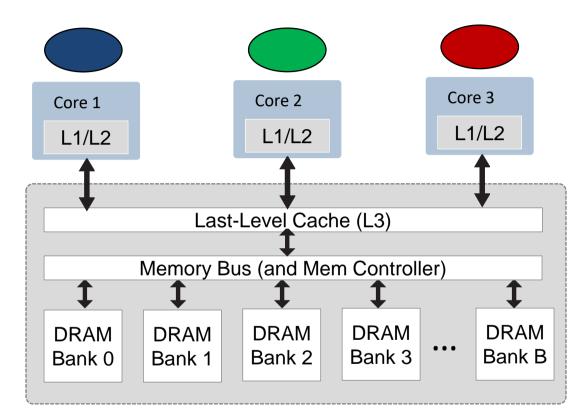

Why is speed sub-additive?

Why is speed sub-additive?

Consider DRAM bank B and its row buffer.

Why is speed sub-additive? Example:

Red task (victim):

1. load address x to register y

2. load address x' to register z

x and x' are in the same row in DRAM bank B' But x and x' are in different columns (different addresses)

Why is speed sub-additive? Example:

Red task:

1. load address x to register y

2. load address x' to register z

Why is speed sub-additive? Example:

Red task:

1. load address x to register y

2. load address x' to register z Green task:

1. load address a (where a is in same bank as x but in different row)

Why is speed sub-additive? Example:

Red task:

1. load address x to register y

2. load address x' to register z Green task:

1. load address a (where a is in same bank as x but in different row)

Blue task:

1. load address b (where b is in same bank as x but in different row)

Why is speed sub-additive? Example:

Red task:

1. load address x to register y

2. load address x' to register z Green task:

1. load address a (where a is in same bank as x but in different row)

Blue task:

1. load address b (where b is in same bank as x but in different row)

Why is speed sub-additive? Example:

Red task:

1. load address x to register y

2. load address x' to register z Green task:

1. load address a (where a is in same bank as x but in different row)

Blue task:

1. load address b (where b is in same bank as x but in different row)

Observation: Green can evict Red's data in the row buffer.

Why is speed sub-additive? Example:

Red task:

1. load address x to register y

2. load address x' to register z Green task:

1. load address a (where a is in same bank as x but in different row)

Blue task:

1. load address b (where b is in same bank as x but in different row)

Observation: Blue can evict Red's data in the row buffer.

Why is speed sub-additive? Example:

Red task:

1. load address x to register y

2. load address x' to register z Green task:

1. load address a (where a is in same bank as x but in different row)

Blue task:

1. load address b (where b is in same bank as x but in different row)

Observation: If Blue has evicted Red's

data in the row buffer, then Green cannot evict it more.

Carnegie Mellon University Timing Analy: Software Engineering Institute <sup>2019</sup>

Why is speed sub-additive? Example:

Red task:

1. load address x to register y

2. load address x' to register z Green task:

1. load address a (where a is in same bank as x but in different row)

Blue task:

1. load address b (where b is in same bank as x but in different row)

Observation: If Green has evicted Red's

data in the row buffer, then Blue cannot evict it more.

Why is speed sub-additive? Example:

Red task:

1. load address x to register y

2. load address x' to register z Green task:

1. load address a (where a is in same bank as x but in different row)

Blue task:

1. load address b (where b is in same bank as x but in different row)

Red experiences a slowdown due to

Blue or Green but the slowdown is not greater by both.

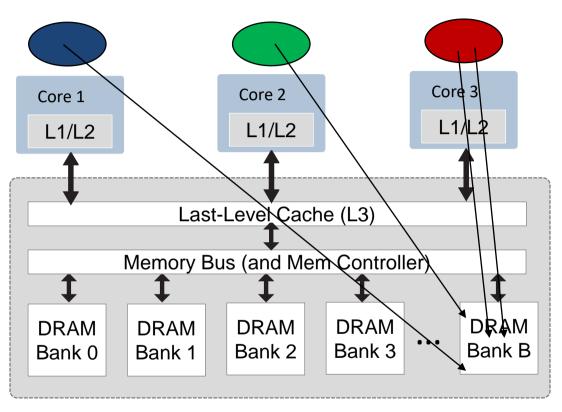

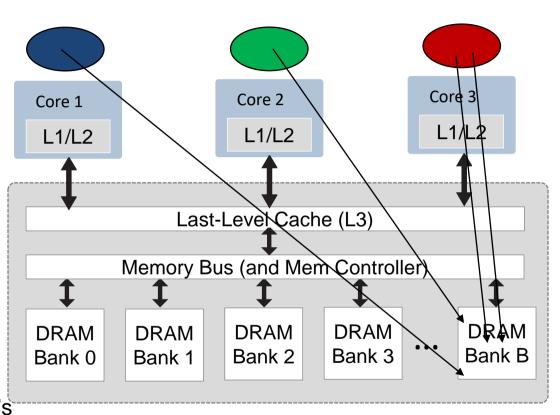

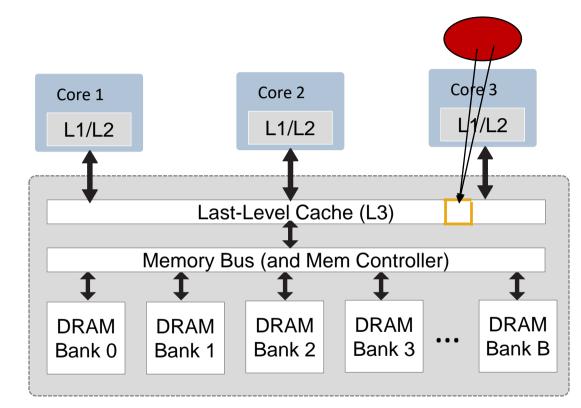

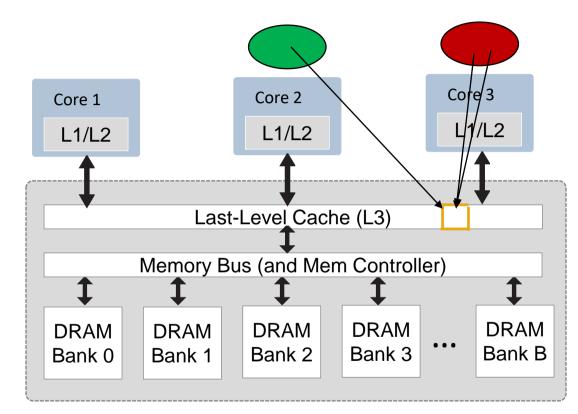

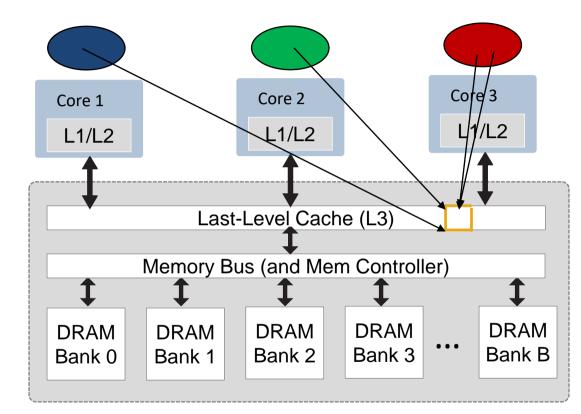

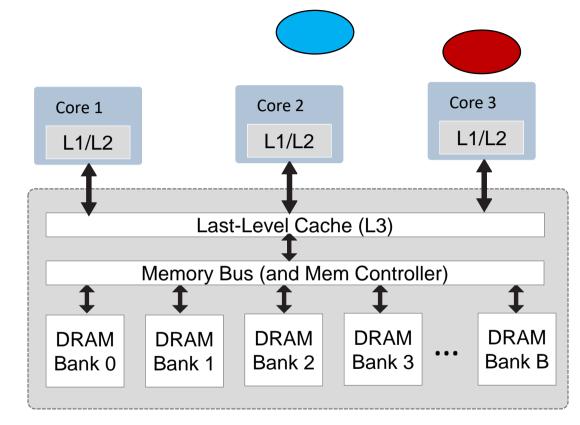

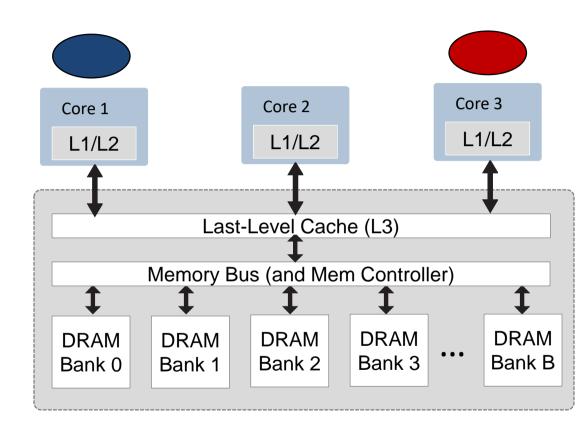

Why is speed super-additive?

Consider Last-Level Cache (L3). Assume associativity = 2. Consider one specific cache set.

Why is speed super-additive?

Example:

Red task (victim):

- 1. load address x to register y

- 2. load address x to register z

Why is speed super-additive?

Example:

Red task (victim):

- 1. load address x to register y

- 2. load address x to register z

Green task:

1. load address a (where a is in same cache set x)

Why is speed super-additive?

Example:

Red task (victim):

- 1. load address x to register y

- 2. load address x to register z

Green task:

1. load address a (where a is in same cache set x)

Observation: Green's data and Red's data fit in the cache. No capacity miss.

Why is speed super-additive?

Example:

Red task (victim):

- 1. load address x to register y

- 2. load address x to register z

Blue task:

- 1. load address b (where b is in same cache set x)

- Observation: Blue's data and Red's data fit in the cache. No capacity miss.

Why is speed super-additive?

Example:

Red task (victim):

- 1. load address x to register y

- 2. load address x to register z Green task:

- 1. load address a (where a is in same cache set x)

Blue task:

1. load address b (where b is in same cache set x)

Observation: Blue's data, Green's data, and Red's data do not fit in the cache. Capacity miss.

Why is speed super-additive?

Example:

Red task (victim):

- 1. load address x to register y

- 2. load address x to register z

- Green task:

- 1. load address a (where a is in same cache set x)

Blue task:

- 1. load address b (where b is in same cache set x)

- Observation: Green alone does not cause slowdown of Red.

Why is speed super-additive?

Example:

Red task (victim):

- 1. load address x to register y

- 2. load address x to register z reen task:

- Green task:

- 1. load address a (where a is in same cache set x)

Blue task:

- 1. load address b (where b is in same cache set x)

- Observation: Blue alone does not cause slowdown of Red.

Why is speed super-additive?

Example:

Red task (victim):

- 1. load address x to register y

- 2. load address x to register z reen task:

- Green task:

- 1. load address a (where a is in same cache set x)

Blue task:

1. load address b (where b is in same cache set x)

Observation: But Green and Blue cause slowdown of Red.

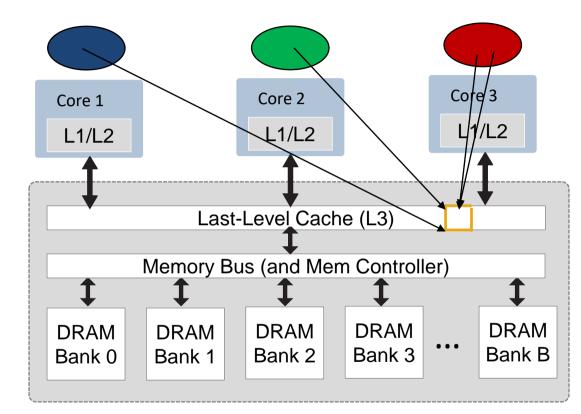

Speed of execution of a task as a function of co-runners can be either

- (i) Additive

- (ii) Sub-additive

- (iii) Super-additive

Speed of execution of a task as a function of co-runners can be either

- (i) Additive

- (ii) Sub-additive

- (iii) Super-additive

If speed is not additive, how can we describe speed as a function of co-runners?

Speed of execution of a task as a function of co-runners can be either

- (i) Additive

- (ii) Sub-additive

- (iii) Super-additive

#### For each task: Enumerate the set of possible co-runner set.

**Carnegie Mellon University** Software Engineering Institute

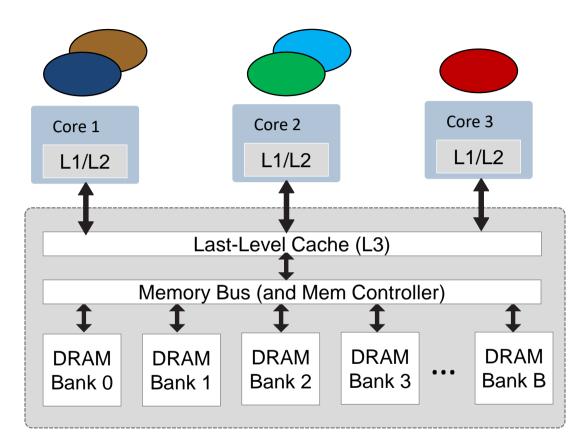

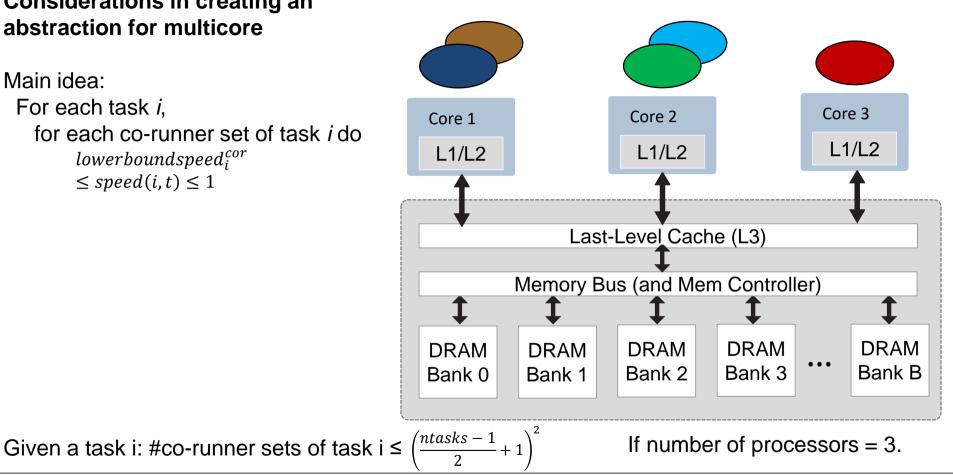

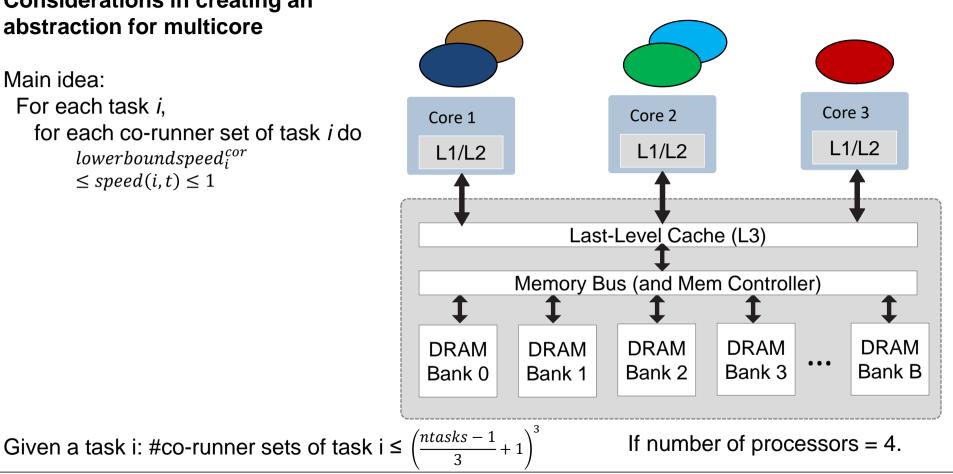

Main idea: For each task *i*, for each co-runner set of task *i* do  $lowerboundspeed_i^{cor}$  $\leq speed(i,t) \leq 1$

#### For each task: Enumerate the set of possible co-runner set.

**Carnegie Mellon University** Software Engineering Institute

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release and unlimited distribution.

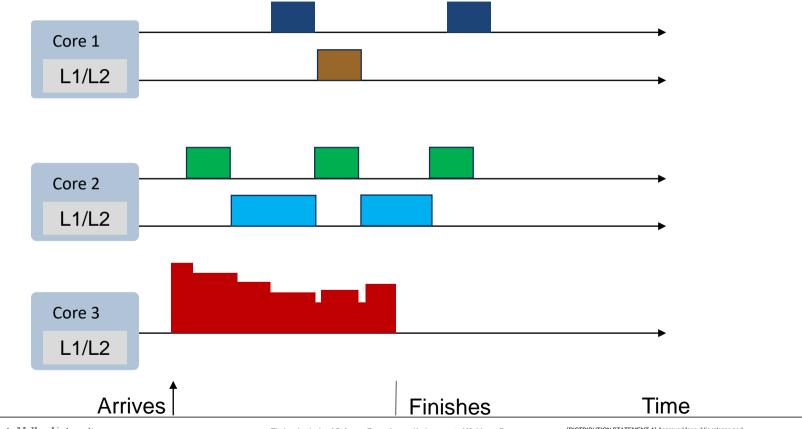

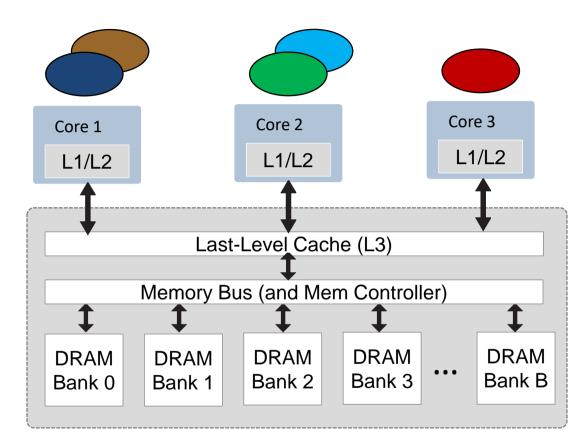

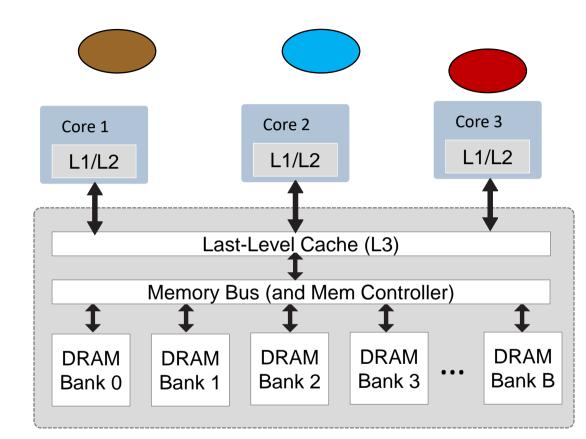

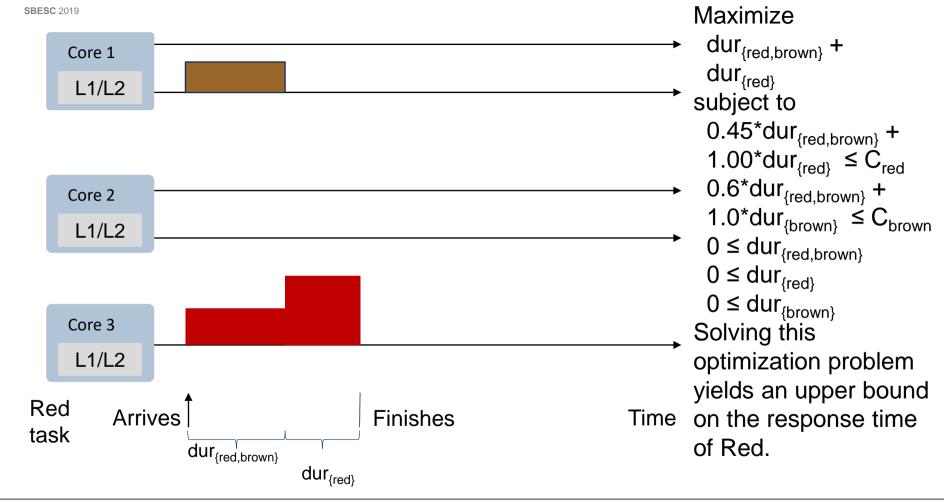

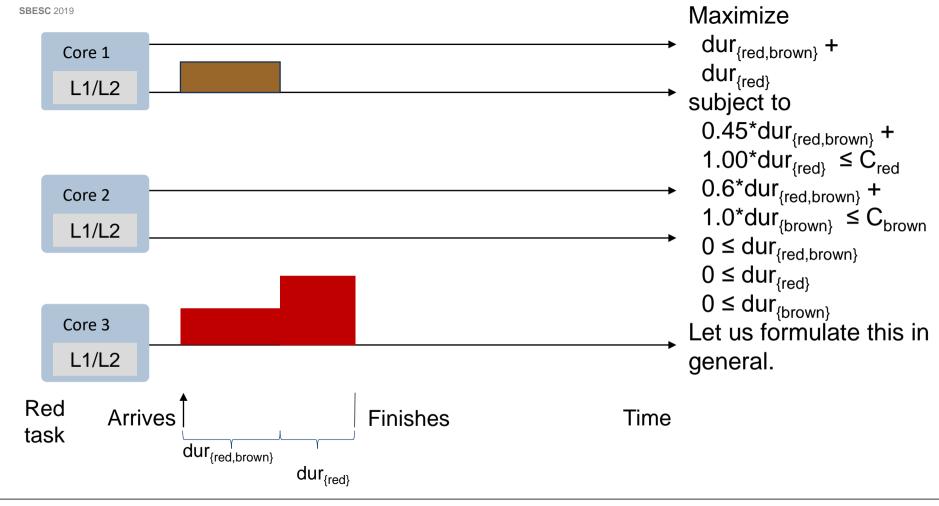

Describing resource consumption of Red task

| C <sub>red</sub> =4 |       |

|---------------------|-------|

| Co-runner set       | Speed |

| {}                  | 1     |

Describing resource consumption of Red task

| C <sub>red</sub> =4 |       |

|---------------------|-------|

| Co-runner set       | Speed |

| {}                  | 1     |

| {cyan}              | 0.5   |

Describing resource consumption of Red task

| C <sub>red</sub> =4 |       |

|---------------------|-------|

| Co-runner set       | Speed |

| {}                  | 1     |

|                     |       |

| {green}             | 0.45  |

Describing resource consumption of Red task

| C <sub>red</sub> =4 |       |

|---------------------|-------|

| Co-runner set       | Speed |

| {}                  | 1     |

|                     |       |

|                     |       |

| {brown}             | 0.45  |

Describing resource consumption of Red task

| Speed |

|-------|

| 1     |

|       |

|       |

|       |

|       |

| 0.25  |

|       |

Describing resource consumption of Red task

| C <sub>red</sub> =4 |  |

|---------------------|--|

| Speed               |  |

| 1                   |  |

|                     |  |

|                     |  |

|                     |  |

|                     |  |

|                     |  |

| 0.18                |  |

|                     |  |

Describing resource consumption of Red task

| C <sub>red</sub> =4 |  |  |  |  |

|---------------------|--|--|--|--|

| Speed               |  |  |  |  |

| 1                   |  |  |  |  |

|                     |  |  |  |  |

|                     |  |  |  |  |

|                     |  |  |  |  |

|                     |  |  |  |  |

|                     |  |  |  |  |

|                     |  |  |  |  |

| 0.12                |  |  |  |  |

|                     |  |  |  |  |

Describing resource consumption of Red task

| C <sub>red</sub> =4 |       |

|---------------------|-------|

| Co-runner set       | Speed |

| {}                  | 1     |

|                     |       |

|                     |       |

|                     |       |

|                     |       |

|                     |       |

|                     |       |

|                     |       |

| {green,brown}       | 0.13  |

Describing resource consumption of Red task

| C <sub>red</sub> =4 |       |  |  |

|---------------------|-------|--|--|

| Co-runner set       | Speed |  |  |

| {}                  | 1     |  |  |

|                     |       |  |  |

|                     |       |  |  |

|                     |       |  |  |

|                     |       |  |  |

|                     |       |  |  |

|                     |       |  |  |

|                     |       |  |  |

|                     |       |  |  |

| {green, blue}       | 0.19  |  |  |

|                     |       |  |  |

Describing resource consumption of Red task

| C <sub>red</sub> =4 |       |  |  |

|---------------------|-------|--|--|

| Co-runner set       | Speed |  |  |

| {}                  | 1     |  |  |

| {cyan}              | 0.5   |  |  |

| {green}             | 0.45  |  |  |

| {brown}             | 0.45  |  |  |

| {blue}              | 0.25  |  |  |

| {cyan, brown}       | 0.18  |  |  |

| {cyan, blue}        | 0.12  |  |  |

| {green,brown}       | 0.13  |  |  |

| {green, blue}       | 0.19  |  |  |

|                     |       |  |  |

Describing resource consumption of Red task

| C <sub>red</sub> =4 |       |

|---------------------|-------|

| Co-runner set       | Speed |

| {}                  | 1     |

| {cyan}              | 0.5   |

| {green}             | 0.45  |

| {brown}             | 0.45  |

| {blue}              | 0.25  |

| {cyan, brown}       | 0.18  |

| {cyan, blue}        | 0.12  |

| {green,brown}       | 0.13  |

| {green, blue}       | 0.19  |

|                     |       |

#### Describe resource consumption of other tasks analogously.

**Carnegie Mellon University** Software Engineering Institute

Main idea: For each task *i*, for each co-runner set of task *i* do  $lowerboundspeed_i^{cor}$  $\leq speed(i,t) \leq 1$

#### For each task: Enumerate the set of possible co-runner set.

#### Isn't that exponential? Couldn't this be bad?

**Carnegie Mellon University** Software Engineering Institute

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release and unlimited distribution.

Main idea: For each task *i*, for each co-runner set of task *i* do *lowerboundspeed*<sup>cor</sup>  $\leq$  speed(*i*, *t*)  $\leq$  1

**Carnegie Mellon University** Software Engineering Institute

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release and unlimited distribution.

Main idea: For each task *i*, for each co-runner set of task *i* do  $lowerboundspeed_i^{cor}$  $\leq speed(i,t) \leq 1$

#### Given a task i: #co-runner sets of task i ≤ polynomial

If number of processors is fixed.

**Carnegie Mellon University** Software Engineering Institute

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release and unlimited distribution.

Main idea: For each task *i*, for each co-runner set of task *i* do  $lowerboundspeed_i^{cor}$  $\leq speed(i,t) \leq 1$

#### Given a task i: #co-runner sets of task i ≤ ntasks

If number of processors = 2.

**Carnegie Mellon University** Software Engineering Institute

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release and unlimited distribution.

Main idea: For each task *i*, for each co-runner set of task *i* do *lowerboundspeed*<sup>cor</sup>  $\leq$  speed(*i*, *t*)  $\leq$  1

**Carnegie Mellon University** Software Engineering Institute

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release and unlimited distribution.

Main idea: For each task *i*, for each co-runner set of task *i* do *lowerboundspeed*<sup>cor</sup>  $\leq$  speed(*i*, *t*)  $\leq$  1

**Carnegie Mellon University** Software Engineering Institute

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release and unlimited distribution.

Given a task *i*: A job of task *i* can experience different co-runner set at different times.

#### **SBESC** 2019

#### How Co-Runners Impact Speed of Execution

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release a unlimited distribution.

#### **SBESC** 2019

### How Co-Runners Impact Speed of Execution

**Carnegie Mellon University** Software Engineering Institute Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release and unlimited distribution.

Given a task *i*: A job of task *i* can experience different co-runner set at different times.

In some computer systems, there are some resources (e.g., memory bus) where the arbitration depends on the processor id of the requestor.

In some computer systems, there are some resources (e.g., memory bus) where the arbitration depends on the processor id of the requestor.

The program behavior may change over time.

The program behavior may change over time.

```

while (1) {

s = wait_until_next_sample()

update_datastructures(s)

a = compute_actuation_command()

actuate_command(a)

```

The program behavior may change over time.

```

while (1) {

s = wait_until_next_sample()

update_datastructures(s)

a = compute_actuation_command()

actuate_command(a)

```

The program behavior here

The program behavior may change over time.

```

while (1) {

s = wait_until_next_sample()

update_datastructures(s)

a = compute_actuation_command()

actuate command(a)

```

The program behavior here

is different from

the program behavior here.

**Carnegie Mellon University** Software Engineering Institute

Timing Analysis of Software Executing on Undocumented Multicore Processors © 2019 Carnegie Mellon University

[DISTRIBUTION STATEMENT A] Approved for public release and unlimited distribution.

The program behavior may change over time.

```

while (1) {

s = wait_until_next_sample()

update_datastructures(s)

a = compute_actuation_command()

actuate_command(a)

```

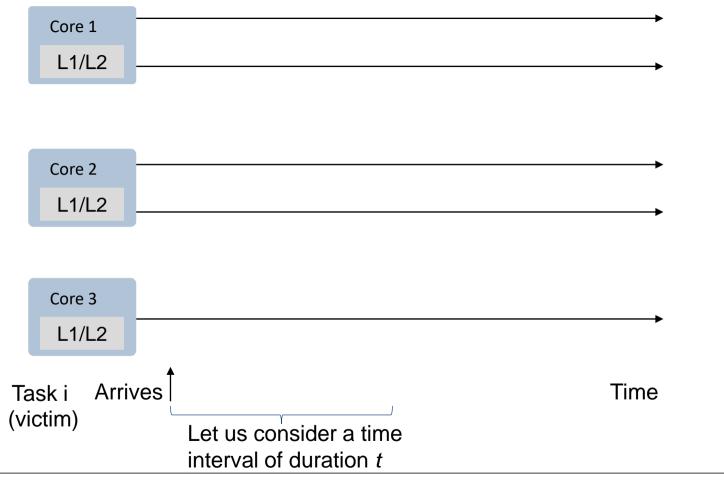

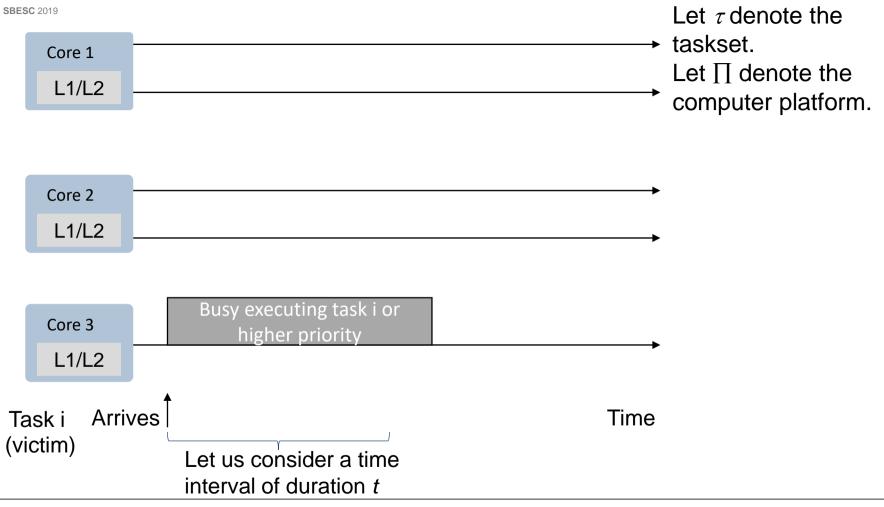

Describe a task as a sequence of segments where each segment may have different description of lower bound on speed as a function of co-runners.

$|\tau| = 5$  procs $(\Pi) = \{P_1, P_2\}$  $T_1 = 1.500 \quad D_1 = 1.500 \quad V_1 = \{v_1^1\} \quad \text{prio}_1 = 3 \quad \text{proc}_1 = 1$ = 0.250  $\text{pd}_1^1$  = 0.500  $\text{CO}_1^1 = \{(\{v_3^1\}, 1.0), (\{v_4^1\}, 0.5), (\{v_5^1\}, 1.0), (\{v_5^2\}, 1.0)\}$  $C_1^1$  $T_2 = 2.000 \quad D_2 = 2.000 \quad V_2 = \{v_2^1\} \quad \text{prio}_2 = 2 \quad \text{proc}_2 = 1$  $C_2^1 = 0.250 \text{ pd}_2^1 = 0.500 \text{ CO}_2^1 = \{(\{v_2^1\}, 0.5), (\{v_4^1\}, 1.0), (\{v_5^1\}, 1.0), (\{v_5^2\}, 1.0)\}$  $T_3 = 2.000 \quad D_3 = 2.000 \quad V_3 = \{v_3^1\} \quad \text{prio}_3 = 3 \quad \text{proc}_3 = 2$  $C_{2}^{1} = 0.250 \text{ pd}_{3}^{1} = 0.500 \text{ CO}_{2}^{1} = \{(\{v_{1}^{1}\}, 1.0), (\{v_{2}^{1}\}, 0.5)\}$  $T_4 = 2.000 \quad D_4 = 2.000 \quad V_4 = \{v_4^1\} \quad \text{prio}_4 = 2 \quad \text{proc}_4 = 2$  $C_4^1 = 0.250 \text{ pd}_4^1 = 0.500 \text{ CO}_4^1 = \{(\{v_1^1\}, 0.5), (\{v_2^1\}, 1.0)\}$  $T_5 = 2.250$   $D_5 = 2.250$   $V_5 = \{v_5^1, v_5^2\}$  prio<sub>5</sub> = 1 proc<sub>5</sub> = 2  $C_5^1 = 0.500 \text{ pd}_5^1 = 1.000 \text{ CO}_5^1 = \{(\{v_1^1\}, 1.0), (\{v_2^1\}, 1.0)\}$  $C_5^2 = 0.125 \text{ pd}_5^2 = 0.500 \text{ CO}_5^2 = \{(\{v_1^1\}, 0.5), (\{v_2^1\}, 1.0)\}$

$|\tau| = 5$  $procs(\Pi) = \{P_1, P_2\}$  $T_1 = 1.500 \quad D_1 = 1.500 \quad V_1 = \{v_1^1\} \quad \text{prio}_1 = 3 \quad \text{proc}_1 = 1$ = 0.250  $\text{pd}_1^1$  = 0.500  $\text{CO}_1^1 = \{(\{v_3^1\}, 1.0), (\{v_4^1\}, 0.5), (\{v_5^1\}, 1.0), (\{v_5^2\}, 1.0)\}$  $C^1$  $T_2 = 2.000 \quad D_2 = 2.000 \quad V_2 = \{v_2^1\} \quad \text{prio}_2 = 2 \quad \text{proc}_2 = 1$  $C_2^1 = 0.250 \text{ pd}_2^1 = 0.500 \text{ CO}_2^1 = \{(\{v_2^1\}, 0.5), (\{v_4^1\}, 1.0), (\{v_5^1\}, 1.0), (\{v_5^2\}, 1.0)\}$  $T_3 = 2.000 \quad D_3 = 2.000 \quad V_3 = \{v_3^1\} \quad \text{prio}_3 = 3 \quad \text{proc}_3 = 2$  $C_{2}^{1} = 0.250 \text{ pd}_{3}^{1} = 0.500 \text{ CO}_{2}^{1} = \{(\{v_{1}^{1}\}, 1.0), (\{v_{2}^{1}\}, 0.5)\}$  $T_4 = 2.000 \quad D_4 = 2.000 \quad V_4 = \{v_4^1\} \quad \text{prio}_4 = 2 \quad \text{proc}_4 = 2$  $C_4^1 = 0.250 \text{ pd}_4^1 = 0.500 \text{ CO}_4^1 = \{(\{v_1^1\}, 0.5), (\{v_2^1\}, 1.0)\}$  $T_5 = 2.250$   $D_5 = 2.250$   $V_5 = \{v_5^1, v_5^2\}$  prio<sub>5</sub> = 1 proc<sub>5</sub> = 2  $C_5^1 = 0.500 \text{ pd}_5^1 = 1.000 \text{ CO}_5^1 = \{(\{v_1^1\}, 1.0), (\{v_2^1\}, 1.0)\}$  $C_5^2 = 0.125 \text{ pd}_5^2 = 0.500 \text{ CO}_5^2 = \{(\{v_1^1\}, 0.5), (\{v_2^1\}, 1.0)\}$

5 Task

#### 2 processors

$$|\tau| = 5$$

procs $(\Pi) = \{P_1, P_2\}$

$$\begin{array}{lll} T_2 &= 2.000 & D_2 &= 2.000 & V_2 = \{v_2^1\} & \text{prio}_2 = 2 & \text{proc}_2 = 1 \\ C_2^1 &= 0.250 & \text{pd}_2^1 &= 0.500 & \text{CO}_2^1 = \{(\{v_3^1\}, 0.5), (\{v_4^1\}, 1.0), (\{v_5^1\}, 1.0), (\{v_5^2\}, 1.0)\} \end{array}$$

$$T_3 = 2.000 \quad D_3 = 2.000 \quad V_3 = \{v_3^1\} \quad \text{prio}_3 = 3 \quad \text{proc}_3 = 2$$

$$C_3^1 = 0.250 \quad \text{pd}_3^1 = 0.500 \quad \text{CO}_3^1 = \{(\{v_1^1\}, 1.0), (\{v_2^1\}, 0.5)\}$$

$$T_4 = 2.000 \quad D_4 = 2.000 \quad V_4 = \{v_4^1\} \quad \text{prio}_4 = 2 \quad \text{proc}_4 = 2$$

$$C_4^1 = 0.250 \quad \text{pd}_4^1 = 0.500 \quad \text{CO}_4^1 = \{(\{v_1^1\}, 0.5), (\{v_2^1\}, 1.0)\}$$

$$T_5 = 2.250 \quad D_5 = 2.250 \quad V_5 = \{v_5^1, v_5^2\} \quad \text{prio}_5 = 1 \quad \text{proc}_5 = 2$$

$$C_5^1 = 0.500 \quad \text{pd}_5^1 = 1.000 \quad \text{CO}_5^1 = \{(\{v_1^1\}, 1.0), (\{v_2^1\}, 1.0)\}$$

$$C_5^2 = 0.125 \quad \text{pd}_5^2 = 0.500 \quad \text{CO}_5^2 = \{(\{v_1^1\}, 0.5), (\{v_2^1\}, 1.0)\}$$

**Carnegie Mellon University** Software Engineering Institute

$|\tau| = 5$  procs $(\Pi) = \{P_1, P_2\}$

$$T_1 = 1.500 \quad D_1 = 1.500 \quad V_1 = \{v_1^1\} \quad \text{prio}_1 = 3 \quad \text{proc}_1 = 1$$

$$C_1^1 = 0.250 \quad \text{pd}_1^1 = 0.500 \quad \text{CO}_1^1 = \{(\{v_3^1\}, 1.0), (\{v_4^1\}, 0.5), (\{v_5^1\}, 1.0), (\{v_5^2\}, 1.0)\}$$

$$T_2 = 2.000 \quad D_2 = 2.000 \quad V_2 = \{v_2^1\} \qquad \text{prio}_2 = 2 \quad \text{proc}_2 = 1$$

$$C_2^1 = 0.250 \text{ pd}_2^1 = 0.500 \text{ CO}_2^1 = \{(\{v_3^1\}, 0.5), (\{v_4^1\}, 1.0), (\{v_5^1\}, 1.0), (\{v_5^2\}, 1.0)\}$$

$$T_3 = 2.000 \quad D_3 = 2.000 \quad V_3 = \{v_3^1\} \quad \text{prio}_3 = 3 \quad \text{proc}_3 = 2$$

$$C_3^1 = 0.250 \quad \text{pd}_3^1 = 0.500 \quad \text{CO}_3^1 = \{(\{v_1^1\}, 1.0), (\{v_2^1\}, 0.5)\}$$

$$T_4 = 2.000 \quad D_4 = 2.000 \quad V_4 = \{v_4^1\} \quad \text{prio}_4 = 2 \quad \text{proc}_4 = 2$$

$$C_4^1 = 0.250 \quad \text{pd}_4^1 = 0.500 \quad \text{CO}_4^1 = \{(\{v_1^1\}, 0.5), (\{v_2^1\}, 1.0)\}$$

$$T_5 = 2.250 \quad D_5 = 2.250 \quad V_5 = \{v_5^1, v_5^2\} \quad \text{prio}_5 = 1 \quad \text{proc}_5 = 2$$

$$C_5^1 = 0.500 \quad \text{pd}_5^1 = 1.000 \quad \text{CO}_5^1 = \{(\{v_1^1\}, 1.0), (\{v_2^1\}, 1.0)\}$$

$$C_5^2 = 0.125 \quad \text{pd}_5^2 = 0.500 \quad \text{CO}_5^2 = \{(\{v_1^1\}, 0.5), (\{v_2^1\}, 1.0)\}$$

**Carnegie Mellon University** Software Engineering Institute Task 1

$|\tau| = 5$  procs( $\Pi$ ) = { $P_1, P_2$ }  $T_1 = 1.500 \quad D_1 = 1.500 \quad V_1 = \{v_1^1\} \quad \text{prio}_1 = 3 \quad \text{proc}_1 = 1$ = 0.250  $\text{pd}_1^1$  = 0.500  $\text{CO}_1^1 = \{(\{v_3^1\}, 1.0), (\{v_4^1\}, 0.5), (\{v_5^1\}, 1.0), (\{v_5^2\}, 1.0)\}$  $C_1^1$  $T_2 = 2.000 \quad D_2 = 2.000 \quad V_2 = \{v_2^1\} \quad \text{prio}_2 = 2 \quad \text{proc}_2 = 1$ Task 2  $= 0.250 \text{ pd}_2^1 = 0.500 \text{ CO}_2^1 = \{(\{v_2^1\}, 0.5), (\{v_4^1\}, 1.0), (\{v_5^1\}, 1.0), (\{v_5^2\}, 1.0)\}$  $C_2^1$  $T_3 = 2.000 \quad D_3 = 2.000 \quad V_3 = \{v_3^1\} \quad \text{prio}_3 = 3 \quad \text{proc}_3 = 2$  $C_{2}^{1} = 0.250 \text{ pd}_{3}^{1} = 0.500 \text{ CO}_{2}^{1} = \{(\{v_{1}^{1}\}, 1.0), (\{v_{2}^{1}\}, 0.5)\}$  $T_4 = 2.000 \quad D_4 = 2.000 \quad V_4 = \{v_4^1\} \quad \text{prio}_4 = 2 \quad \text{proc}_4 = 2$  $C_4^1 = 0.250 \text{ pd}_4^1 = 0.500 \text{ CO}_4^1 = \{(\{v_1^1\}, 0.5), (\{v_2^1\}, 1.0)\}$  $T_5 = 2.250$   $D_5 = 2.250$   $V_5 = \{v_5^1, v_5^2\}$  prio<sub>5</sub> = 1 proc<sub>5</sub> = 2  $C_5^1 = 0.500 \text{ pd}_5^1 = 1.000 \text{ CO}_5^1 = \{(\{v_1^1\}, 1.0), (\{v_2^1\}, 1.0)\}$  $C_5^2 = 0.125 \text{ pd}_5^2 = 0.500 \text{ CO}_5^2 = \{(\{v_1^1\}, 0.5), (\{v_2^1\}, 1.0)\}$

| $ \tau  = 5$    | $\operatorname{procs}(\Pi) = \{P$ | $P_1, P_2$ }                                                                                                                                                                                                   |        |

|-----------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                 |                                   | $\begin{split} V_1 &= \{v_1^1\} & \text{prio}_1 = 3 & \text{proc}_1 = 1 \\ \text{CO}_1^1 &= \{(\{v_3^1\}, 1.0), (\{v_4^1\}, 0.5), (\{v_5^1\}, 1.0), (\{v_5^2\}, 1.0)\} \end{split}$                            |        |

|                 |                                   | $V_2 = \{v_2^1\}  \text{prio}_2 = 2  \text{proc}_2 = 1$<br>$CO_2^1 = \{(\{v_3^1\}, 0.5), (\{v_4^1\}, 1.0), (\{v_5^1\}, 1.0), (\{v_5^2\}, 1.0)\}$                                                               | _      |

|                 |                                   | $V_3 = \{v_3^1\}  \text{prio}_3 = 3  \text{proc}_3 = 2$ $CO_3^1 = \{(\{v_1^1\}, 1.0), (\{v_2^1\}, 0.5)\}$                                                                                                      | Task 3 |

|                 |                                   | $V_4 = \{v_4^1\}  \text{prio}_4 = 2  \text{proc}_4 = 2$<br>$CO_4^1 = \{(\{v_1^1\}, 0.5), (\{v_2^1\}, 1.0)\}$                                                                                                   |        |

| $C_5^1 = 0.500$ | $pd_5^1 = 1.000$                  | $V_{5} = \{v_{5}^{1}, v_{5}^{2}\} \text{ prio}_{5} = 1 \text{ proc}_{5} = 2$<br>$CO_{5}^{1} = \{(\{v_{1}^{1}\}, 1.0), (\{v_{2}^{1}\}, 1.0)\}$<br>$CO_{5}^{2} = \{(\{v_{1}^{1}\}, 0.5), (\{v_{2}^{1}\}, 1.0)\}$ |        |

$|\tau| = 5$  procs( $\Pi$ ) = { $P_1, P_2$ }  $T_1 = 1.500 \quad D_1 = 1.500 \quad V_1 = \{v_1^1\} \quad \text{prio}_1 = 3 \quad \text{proc}_1 = 1$ = 0.250  $\text{pd}_1^1$  = 0.500  $\text{CO}_1^1 = \{(\{v_3^1\}, 1.0), (\{v_4^1\}, 0.5), (\{v_5^1\}, 1.0), (\{v_5^2\}, 1.0)\}$  $C_1^1$  $T_2 = 2.000 \quad D_2 = 2.000 \quad V_2 = \{v_2^1\} \quad \text{prio}_2 = 2 \quad \text{proc}_2 = 1$  $C_2^1 = 0.250 \text{ pd}_2^1 = 0.500 \text{ CO}_2^1 = \{(\{v_3\}, 0.5), (\{v_4\}, 1.0), (\{v_5\}, 1.0), (\{v_5\}, 1.0)\}$  $T_3 = 2.000 \quad D_3 = 2.000 \quad V_3 = \{v_3^1\} \quad \text{prio}_3 = 3 \quad \text{proc}_3 = 2$  $C_{2}^{1} = 0.250 \text{ pd}_{3}^{1} = 0.500 \text{ CO}_{2}^{1} = \{(\{v_{1}^{1}\}, 1.0), (\{v_{2}^{1}\}, 0.5)\}$  $T_4 = 2.000 \quad D_4 = 2.000 \quad V_4 = \{v_4^1\} \quad \text{prio}_4 = 2 \quad \text{proc}_4 = 2$  $C^1_4$  $= 0.250 \text{ pd}_4^1 = 0.500 \text{ CO}_4^1 = \{(\{v_1^1\}, 0.5), (\{v_2^1\}, 1.0)\}$  $T_5 = 2.250$   $D_5 = 2.250$   $V_5 = \{v_5^1, v_5^2\}$  prio<sub>5</sub> = 1 proc<sub>5</sub> = 2  $C_5^1 = 0.500 \text{ pd}_5^1 = 1.000 \text{ CO}_5^1 = \{(\{v_1^1\}, 1.0), (\{v_2^1\}, 1.0)\}$  $C_5^2 = 0.125 \text{ pd}_5^2 = 0.500 \text{ CO}_5^2 = \{(\{v_1^1\}, 0.5), (\{v_2^1\}, 1.0)\}$

**Carnegie Mellon University** Software Engineering Institute Task 4

$|\tau| = 5$  procs $(\Pi) = \{P_1, P_2\}$  $T_1 = 1.500 \quad D_1 = 1.500 \quad V_1 = \{v_1^1\} \quad \text{prio}_1 = 3 \quad \text{proc}_1 = 1$  $= 0.250 \text{ pd}_1^1 = 0.500 \text{ CO}_1^1 = \{(\{v_3^1\}, 1.0), (\{v_4^1\}, 0.5), (\{v_5^1\}, 1.0), (\{v_5^2\}, 1.0)\}$  $C_1^1$  $T_2 = 2.000 \quad D_2 = 2.000 \quad V_2 = \{v_2^1\} \quad \text{prio}_2 = 2 \quad \text{proc}_2 = 1$  $C_2^1 = 0.250 \text{ pd}_2^1 = 0.500 \text{ CO}_2^1 = \{(\{v_3\}, 0.5), (\{v_4\}, 1.0), (\{v_5\}, 1.0), (\{v_5\}, 1.0)\}$  $T_3 = 2.000 \quad D_3 = 2.000 \quad V_3 = \{v_3^1\} \quad \text{prio}_3 = 3 \quad \text{proc}_3 = 2$  $C_{2}^{1} = 0.250 \text{ pd}_{3}^{1} = 0.500 \text{ CO}_{2}^{1} = \{(\{v_{1}^{1}\}, 1.0), (\{v_{2}^{1}\}, 0.5)\}$  $T_4 = 2.000 \quad D_4 = 2.000 \quad V_4 = \{v_4^1\} \quad \text{prio}_4 = 2 \quad \text{proc}_4 = 2$  $C_4^1 = 0.250 \text{ pd}_4^1 = 0.500 \text{ CO}_4^1 = \{(\{v_1^1\}, 0.5), (\{v_2^1\}, 1.0)\}$  $T_5 = 2.250$   $D_5 = 2.250$   $V_5 = \{v_5^1, v_5^2\}$  prio<sub>5</sub> = 1 proc<sub>5</sub> = 2  $C_5^1 = 0.500 \text{ pd}_5^1 = 1.000 \text{ CO}_5^1 = \{(\{v_1^1\}, 1.0), (\{v_2^1\}, 1.0)\}$  $= 0.125 \text{ pd}_5^2 = 0.500 \text{ CO}_5^2 = \{(\{v_1^1\}, 0.5), (\{v_2^1\}, 1.0)\}$  $C_{5}^{2}$

Task 5

**Carnegie Mellon University** Software Engineering Institute

| $ \tau  = 5$ $\operatorname{procs}(\Pi) = \{P_1, P_2\}$<br>Minimum inter-arrival times of tasks |         |                   |         |                                                                                                                                                                     |                      |                                                               |

|-------------------------------------------------------------------------------------------------|---------|-------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------|

|                                                                                                 |         |                   |         | $V_1 = \{v_1^1\} \\ CO_1^1 = \{(\{v_3^1\}, $                                                                                                                        |                      | $proc_1 = 1$<br>0.5), ({ $v_5^1$ }, 1.0), ({ $v_5^2$ }, 1.0)} |