1

#1

## Nikil D. Dutt<sup>1</sup>

Center for Embedded and Cyber-Physical Systems (CECS) University of California, Irvine dutt@uci.edu <u>http://www.ics.uci.edu/~dutt</u> <u>https://duttgroup.ics.uci.edu</u>

<sup>1</sup> Joint work with Santanu Sarma and Dutt Research Group

Research Partially Supported by the NSF Variability Expedition Project

Copyright © 2014 Dutt Research Group

https://duttgroup.ics.uci.edu

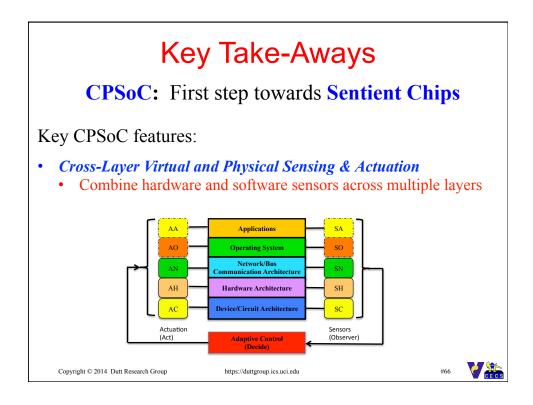

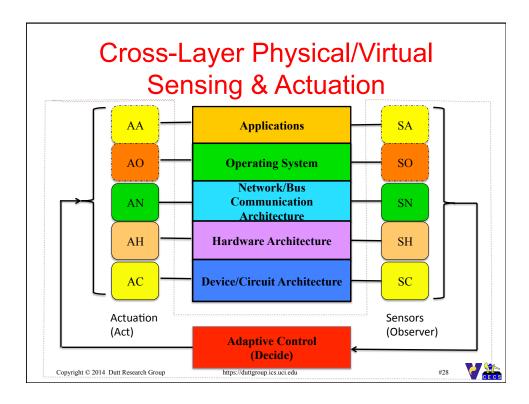

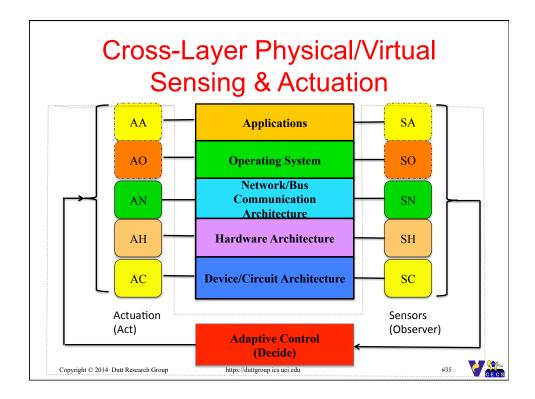

## Examples of Virtual Sensors and Actuators Across Layers of CPSoC

| Layers                       | Virtual/Physical Sensors                                                             | Virtual/Physical Actuators                                                        |

|------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Application                  | Execution Time, Workload Power, Energy,                                              | Loop perforation<br>Algorithmic Choice                                            |

| Operating<br>System          | System Utilization<br>Peripheral States                                              | Task Allocation, Scheduling,<br>Migration, Duty Cycling                           |

| Network/Bus<br>Communication | Bandwidth; Packet/Flit status;<br>Channel Status, Congestion,<br>Latency             | Adaptive Routing<br>Dynamic Bandwidth Allocation<br>Ch. no and direction          |

| Hardware<br>Architecture     | Cache misses, Miss rate; access<br>rate; IPC, Throughput, ILP/MLP,<br>Core asymmetry | Cache Sizing; Reconfiguration,<br>Resource Provision<br>Static/Dynamic Redundancy |

| Circuit/Device               | Circuit Delay, Aging, leakage<br>Temperature, oxide breakdown                        | DVFS, DFS, DVS ABB, Clock and Power-gating                                        |

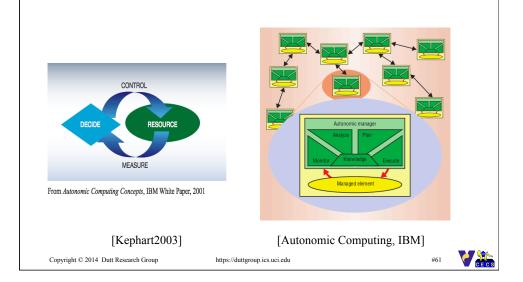

## Self-\* Computing: Related Efforts

- Autonomic Computing (IBM)

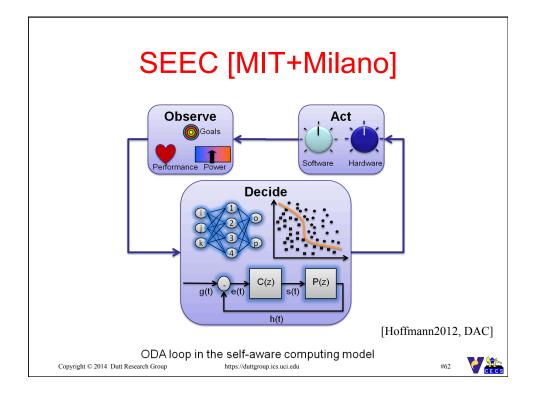

- SEEC (MIT & Milano)

- Software centric/focused adaptation with homogeneous arch

- Uses ODA loop for feedback control

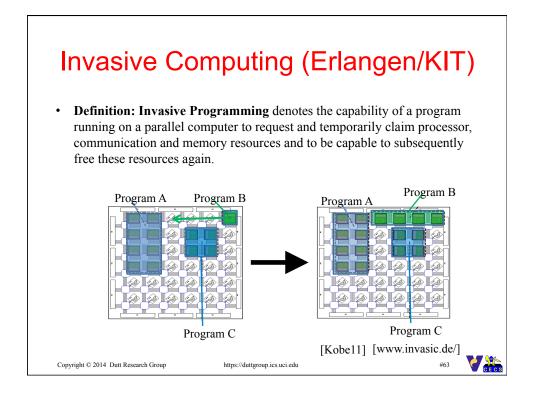

- Invasive Computing (Erlangen & KIT)

- Adaptive use of computing platform resources

- Distributed management

- No Self-modeling and system behavior identification

https://duttgroup.ics.uci.edu

V

#60

## Self-Awareness in Software Systems (IBM's Autonomic Computing)